- 您现在的位置:买卖IC网 > PDF目录97867 > DS2181AQ (DALLAS SEMICONDUCTOR) DATACOM, FRAMER, PQCC44 PDF资料下载

参数资料

| 型号: | DS2181AQ |

| 厂商: | DALLAS SEMICONDUCTOR |

| 元件分类: | Digital Transmission Controller |

| 英文描述: | DATACOM, FRAMER, PQCC44 |

| 封装: | PLASTIC, LCC-44 |

| 文件页数: | 6/32页 |

| 文件大小: | 377K |

| 代理商: | DS2181AQ |

第1页第2页第3页第4页第5页当前第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

DS2181A

14 of 32

Bits 4 through 8 of timeslot 0 in non-align frames are reserved for national use. When TCR.3 = 1, the

transmitted national bits are sourced from register locations TINR.4 through TINR.0. If TCR.3 = 0, the

national bits are sampled at TIND during bit times 4 through 8 of timeslot 0 in non-align frames.

Reserved bit positions in the TINR must be set to 0 when written; those bits can be 0 or 1 when read.

TXR: TRANSMIT EXTRA REGISTER Figure 10

(MSB)

(LSB)

-

XB1

TDMA

XB2

XB3

SYMBOL

POSITION

NAME AND DESCRIPTION

-

TXR.7

Reserved; must be 0 for proper operation.

-

TXR.6

Reserved; must be 0 for proper operation.

-

TXR.5

Reserved; must be 0 for proper operation.

-

TXR.4

Reserved; must be 0 for proper operation.

XB1

TXR.3

Extra Bit 1

TDMA

TXR.2

Transmit Distant Multiframe Alarm

0 = Normal operation; bit 6 of timeslot 16 in frame 0 clear.

1 = Alarm condition; bit 6 of timeslot 16 in frame 0 set.

XB2

TXR.1

Extra Bit 2

XB3

TXR.0

Extra Bit 3

TRANSMIT EXTRA DATA

In the CAS mode, timeslot 16 of frame 0 contains the multiframe alignment pattern, extra bits and the

distant multiframe alarm. When CAS is enabled (TCR.5 = 0), the extra bits are sourced from TXR.0,

TXR.1 and TXR.3 (TCR.2 = 1) or the extra bits are sampled externally at TXD during the extra bit time

(TCR.2 = 0). The extra bits, alignment pattern and alarm signal are not utilized in the CCS mode (TCR.5

= 1); input TSER overwrites all timeslot 16 bit positions.

Reserved bit positions in the TXR must be set to 0 when written; those bits can be 0 or 1 when read.

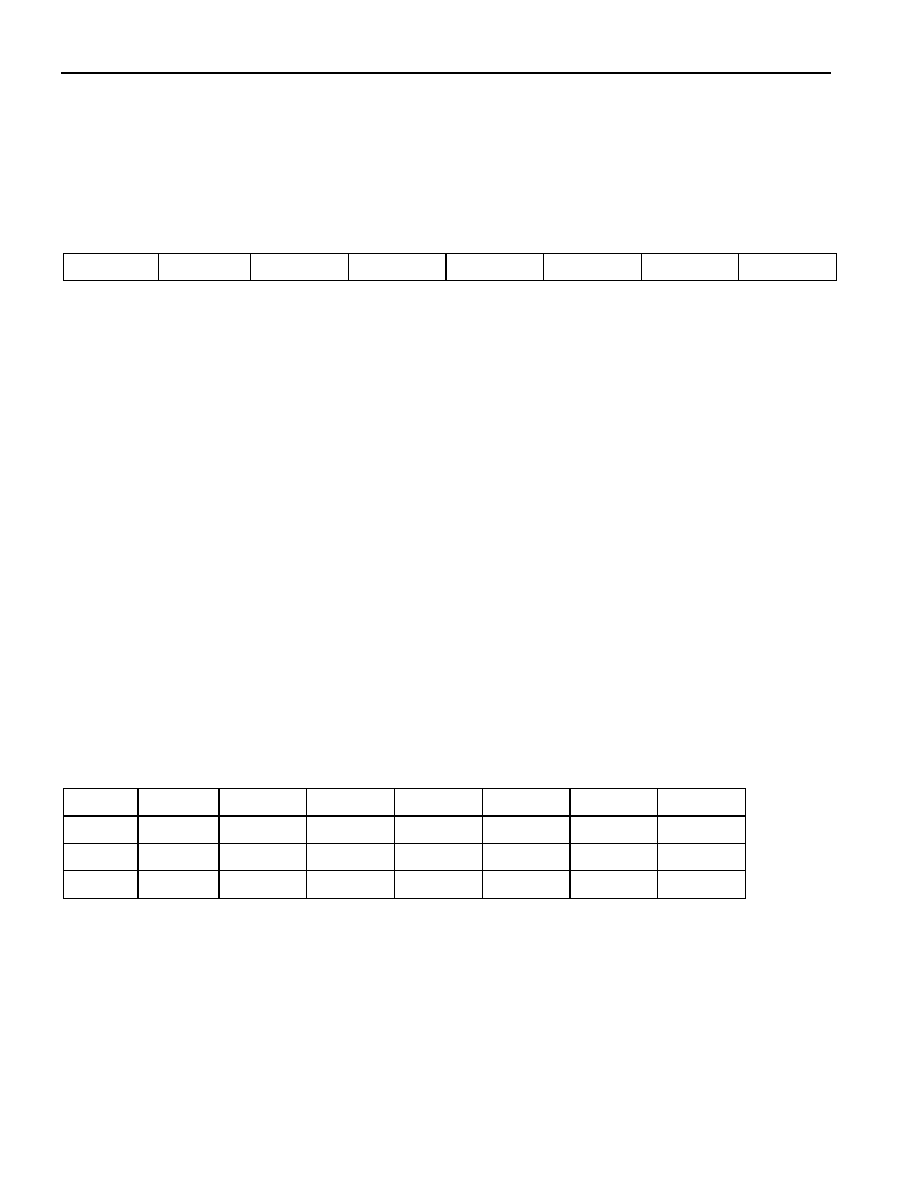

TIR1 - TIR4: TRANSMIT IDLE REGISTERS Figure 11

(MSB)

(LSB)

TS7

TS6

TS5

TS4

TS3

TS2

TS1

TS0

1

TIR1

TS15

TS14

TS13

TS12

TS11

TS10

TS9

TS8

TIR2

TS23

TS22

TS21

TS20

TS19

TS18

TS17

TS16

1

TIR3

TS31

TS30

TS29

TS28

TS27

TS26

TS25

TS024

TIR4

SYMBOL

POSITION

NAME AND DESCRIPTION

TS31

TIR4.7

Transmit Idle Registers

TS0

TIR1.0

Each of these bit positions represents a timeslot in the outgoing

stream at TPOS and TNEG; when set, the contents of that timeslot

are forced to idle code (11010101).

NOTE:

1. TS0 and TS16 are not affected by the idle register.

相关PDF资料 |

PDF描述 |

|---|---|

| DS2182A | DATACOM, FRAMER, PDIP28 |

| DS2186S | DATACOM, DIGITAL SLIC, PDSO20 |

| DS2187 | DATACOM, PCM TRANSCEIVER, PDIP18 |

| DS2196LN | DATACOM, FRAMER, PQFP100 |

| DS21FF44 | DATACOM, FRAMER, PBGA300 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 534AB000129DG | 功能描述:IC CLK XO QUAD FREQUENCY 8SMD RoHS:是 类别:晶体和振荡器 >> 振荡器 - 可配置引脚 系列:Si534 应用说明:Frequency Margining using the SI534 标准包装:50 系列:Si534 类型:XO(标准) 频率 - 输出 1:11.29MHz,12.29Mhz,22.58Mhz,24.58MHz 频率 - 输出 2:单输出 输出:LVPECL 电源电压:2.97 V ~ 3.63 V 封装/外壳:8-QFN 包装:托盘 功能:三态(输出启用) 频率稳定性:±7ppm 电流 - 电源(最大):121mA 电流 - 电源(禁用)(最大):- 工作温度:-40°C ~ 85°C 尺寸/尺寸:0.276" L x 0.197" W(7.00mm x 5.00mm) 高度:0.071"(1.80mm) 其它名称:Q5356778 |

| 534AB000240DG | 制造商:Silicon Laboratories Inc 功能描述:SMD CRYSTAL OSC 450MHZ/580MHZ/625MHZ/640MHZ 3.3V 6PIN - Trays |

| 534AB000287DG | 制造商:Silicon Laboratories Inc 功能描述:SMD CRYSTAL OSC 850MHZ/900MHZ/940MHZ/1GHZ 3.3V 6PIN - Trays |

| 534AB000287DGR | 制造商:Silicon Laboratories Inc 功能描述:SMD CRYSTAL OSC 850MHZ/900MHZ/940MHZ/1GHZ 3.3V 6PIN - Tape and Reel |

| 534AB000289DG | 制造商:Silicon Laboratories Inc 功能描述:SMD CRYSTAL OSC 155.52MHZ/161.13281MHZ/167.331712MHZ/173.370 - Trays |

发布紧急采购,3分钟左右您将得到回复。