- 您现在的位置:买卖IC网 > PDF目录379698 > ATT3042-50S132I (Electronic Theatre Controls, Inc.) Field-Programmable Gate Arrays PDF资料下载

参数资料

| 型号: | ATT3042-50S132I |

| 厂商: | Electronic Theatre Controls, Inc. |

| 元件分类: | FPGA |

| 英文描述: | Field-Programmable Gate Arrays |

| 中文描述: | 现场可编程门阵列 |

| 文件页数: | 18/80页 |

| 文件大小: | 528K |

| 代理商: | ATT3042-50S132I |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页当前第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页

Data Sheet

February 1997

ATT3000 Series Field-Programmable Gate Arrays

18

Lucent Technologies Inc.

Configuration

(continued)

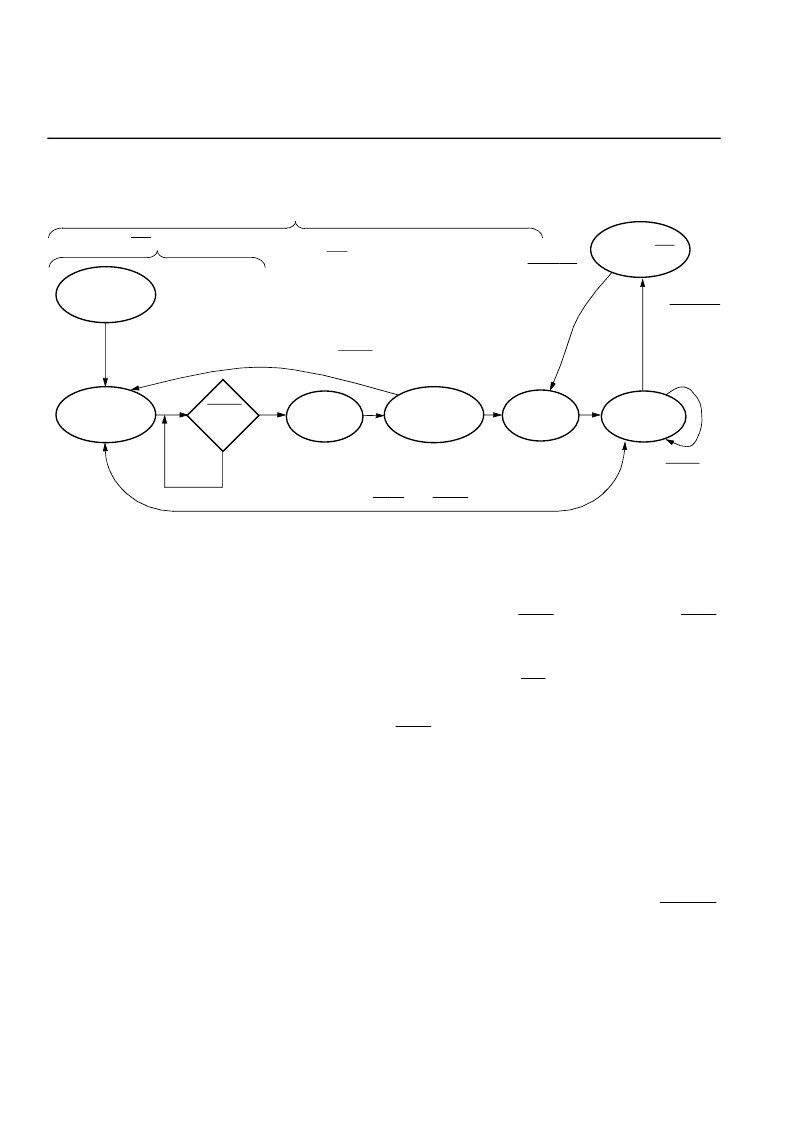

Figure 18. State Diagram of Configuration Process for Powerup and Reprogram

5-3110(F)

INITIALIZATION

POWER-ON

TIME DELAY

CLEAR

CONFIGURATION

MEMORY

YES

RESET

ACTIVE

NO

TEST

MODE PINS

CONFIGURATION

PROGRAM MODE

OPERATIONAL

MODE

START-UP

INIT = LOW

USER I/O PINS WITH HIGH-IMPEDANCE PULL-UP

HDC = HIGH

LDC = LOW

ACTIVE RESET

POWERDOWN

NO HDC, LDC

OR PULL-UP

INACTIVE

PWRDWN

ACTIVE RESET

OPERATES ON

USER LOGIC

LOW ON DONE/PROG AND RESET

ACTIVE

PWRDWN

Length count control allows a system of multiple

FPGAs in assorted sizes to begin operation in a syn-

chronized fashion. The configuration program gener-

ated by the

ORCA

Foundry Development System

begins with a preamble of 111111110010 (binary), fol-

lowed by a 24-bit length count representing the total

number of configuration clocks needed to complete

loading of the configuration program(s). The data fram-

ing is shown in Figure 19. All FPGAs connected in

series read and shift preamble and length count in (on

positive) and out (on negative) CCLK edges. An FPGA

which has received the preamble and length count then

presents a HIGH data out until it has intercepted the

appropriate number of data frames. When the configu-

ration program memory of an FPGA is full and the

length count does not compare, the FPGA shifts any

additional data through, as it did for preamble and

length count.

When the FPGA configuration memory is full and the

length count compares, the FPGA will execute a syn-

chronous start-up sequence and become operational

(see Figure 20 on page 20). Two CCLK cycles after the

completion of loading configuration data, the user

I/O pins are enabled as configured. As selected in

ORCA

Foundry, the internal user-logic reset is released

either one clock cycle before or after the I/O pins

become active. A similar timing selection is program-

mable for the DONE/

PROG

output signal. DONE/

PROG

may also be programmed to be an open drain or

include a pull-up resistor to accommodate wired-

ANDing. The high during configuration (HDC) and low

during configuration (

LDC

) are two user I/O pins which

are driven active when an FPGA is in initialization,

clear, or configure states. These signals and DONE/

PROG

provide for control of external logic signals such

as reset, bus enable, or PROM enable during

configuration.

For parallel master configuration modes, these signals

provide PROM enable control and allow the data pins

to be shared with user logic signals.

User I/O inputs can be programmed to be either TTL or

CMOS compatible thresholds. At powerup, all inputs

have TTL thresholds and can change to CMOS thresh-

olds at the completion of configuration, if the user has

selected CMOS thresholds. The threshold of

PWRDWN

and the direct clock inputs are fixed at a CMOS level.

If the crystal oscillator is used, it will begin operation

before configuration is complete to allow time for

stabilization before it is connected to the internal

circuitry.

相关PDF资料 |

PDF描述 |

|---|---|

| ATT3042-50S44I | Field-Programmable Gate Arrays |

| ATT3042-50S68I | Field-Programmable Gate Arrays |

| ATT3042-50S84I | Field-Programmable Gate Arrays |

| ATT3042-50T132I | Field-Programmable Gate Arrays |

| ATT3042-50T44I | Field-Programmable Gate Arrays |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ATT3042-50S44I | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field-Programmable Gate Arrays |

| ATT3042-50S68I | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field-Programmable Gate Arrays |

| ATT3042-50S84I | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field-Programmable Gate Arrays |

| ATT3042-50T132I | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field-Programmable Gate Arrays |

| ATT3042-50T44I | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field-Programmable Gate Arrays |

发布紧急采购,3分钟左右您将得到回复。