- 您现在的位置:买卖IC网 > PDF目录379992 > COP8SGR628N8 (National Semiconductor Corporation) 8-Bit CMOS ROM Based and OTP Microcontrollers with 8k to 32k Memory, Two Comparators and USART PDF资料下载

参数资料

| 型号: | COP8SGR628N8 |

| 厂商: | National Semiconductor Corporation |

| 英文描述: | 8-Bit CMOS ROM Based and OTP Microcontrollers with 8k to 32k Memory, Two Comparators and USART |

| 中文描述: | 8位的CMOS基于ROM和OTP微控制器具有8K到32K的内存,2个比较器和USART |

| 文件页数: | 14/62页 |

| 文件大小: | 913K |

| 代理商: | COP8SGR628N8 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页

4.0 Pin Descriptions

The COP8SGx I/O structure enables designers to reconfig-

ure the microcontroller’s I/O functions with a single instruc-

tion. Each individual I/O pin can be independently configured

as output pin low, output high, input with high impedance or

input with weak pull-up device. A typical example is the use

of I/O pins as the keyboard matrix input lines. The input lines

can be programmed with internal weak pull-ups so that the

input lines read logic high when the keys are all open. With

a key closure, the corresponding input line will read a logic

zero since the weak pull-up can easily be overdriven. When

the key is released, the internal weak pull-up will pull the

input line back to logic high. This eliminates the need for

external pull-up resistors. The high current options are avail-

able for driving LEDs, motors and speakers. This flexibility

helps to ensure a cleaner design, with less external compo-

nents and lower costs. Below is the general description of all

available pins.

V

and GND are the power supply pins. All V

CC

and GND

pins must be connected.

CKI is the clock input. This can come from the Internal R/C

oscillator, external, or a crystal oscillator (in conjunction with

CKO). See Oscillator Description section.

RESET is the master reset input. See Reset description

section.

Each device contains four bidirectional 8-bit I/O ports (C, G,

L and F), where each individual bit may be independently

configured as an input (Schmitt trigger inputs on ports L and

G), output or TRI-STATE under program control. Three data

memory address locations are allocated for each of these

I/O ports. Each I/O port has two associated 8-bit memory

mapped registers, the CONFIGURATION register and the

output DATA register. A memory mapped address is also

reserved for the input pins of each I/O port. (See the memory

map for the various addresses associated with the I/O ports.)

Figure 4 shows the I/O port configurations. The DATA and

CONFIGURATION registers allow for each port bit to be

individually configured under software control as shown be-

low:

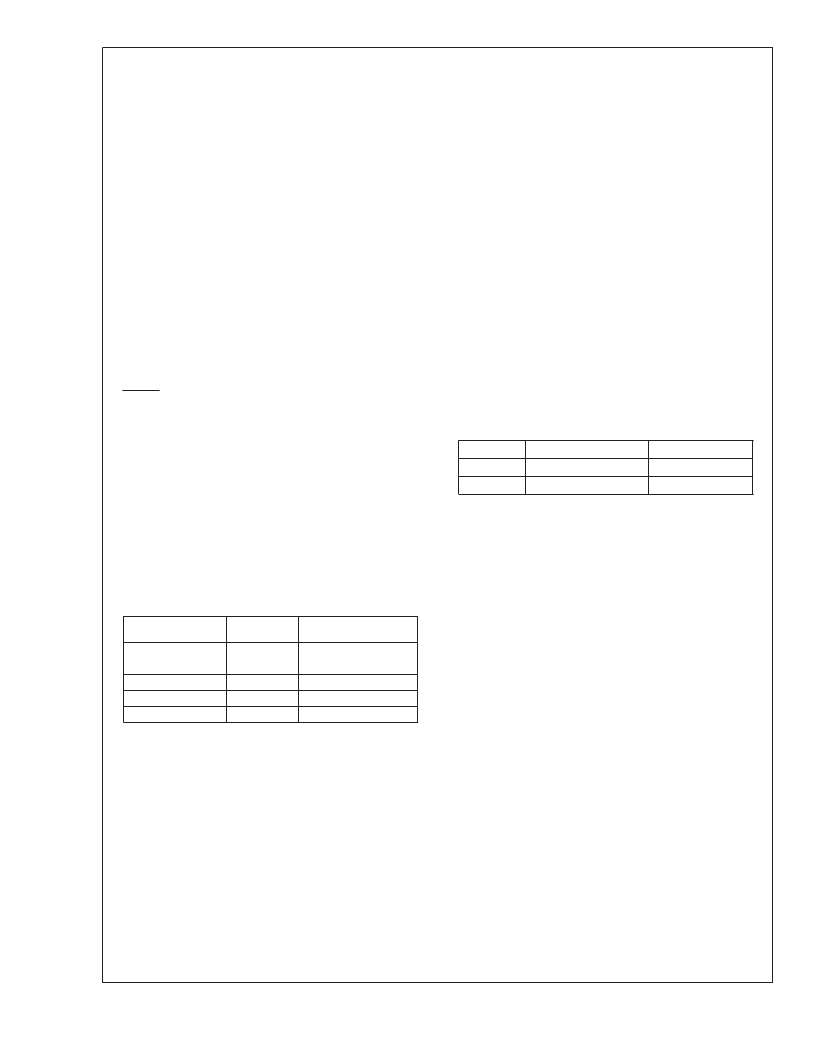

CONFIGURATION

Register

0

DATA

Register

0

Port Set-Up

Hi-Z Input

(TRI-STATE Output)

Input with Weak Pull-Up

Push-Pull Zero Output

Push-Pull One Output

0

1

1

1

0

1

Port L is an 8-bit I/O port. All L-pins have Schmitt triggers on

the inputs.

Port L supports the Multi-Input Wake Up feature on all eight

pins. Port L has the following alternate pin functions:

L7 Multi-input Wakeup or T3B (Timer T3B Input)

L6 Multi-input Wakeup or T3A (Timer T3A Input)

L5 Multi-input Wakeup or T2B (Timer T2B Input)

L4 Multi-input Wakeup or T2A (Timer T2A Input)

L3 Multi-input Wakeup and/or RDX (USART Receive)

L2 Multi-input Wakeup or TDX (USART Transmit)

L1 Multi-input Wakeup and/or CKX (USART Clock)

L0 Multi-input Wakeup

Port G is an 8-bit port. Pin G0, G2–G5 are bi-directional I/O

ports. Pin G6 is always a general purpose Hi-Z input. All pins

have Schmitt Triggers on their inputs.

Pin G1 serves as the

dedicated WATCHDOG output with weak pullup if

WATCHDOG feature is selected by the Mask Option reg-

ister. The pin is a general purpose I/O if WATCHDOG

feature is not selected.

If WATCHDOG feature is selected,

bit 1 of the Port G configuration and data register does not

have any effect on Pin G1 setup. Pin G7 is either input or

output depending on the oscillator option selected. With the

crystal oscillator option selected, G7 serves as the dedicated

output pin for the CKO clock output. With the internal R/C or

the external oscillator option selected, G7 serves as a gen-

eral purpose Hi-Z input pin and is also used to bring the

device out of HALT mode with a low to high transition on G7.

Since G6 is an input only pin and G7 is the dedicated CKO

clock output pin (crystal clock option) or general purpose

input (R/C or external clock option), the associated bits in the

data and configuration registers for G6 and G7 are used for

special purpose functions as outlined below. Reading the G6

and G7 data bits will return zeroes.

Each device will be placed in the HALT mode by writing a “1”

to bit 7 of the Port G Data Register. Similarly the device will

be placed in the IDLE mode by writing a “1” to bit 6 of the

Port G Data Register.

Writing a “1” to bit 6 of the Port G Configuration Register

enables the MICROWIRE/PLUS to operate with the alter-

nate phase of the SK clock. The G7 configuration bit, if set

high, enables the clock start up delay after HALT when the

R/C clock configuration is used.

Config. Reg.

CLKDLY

Alternate SK

Data Reg.

HALT

IDLE

G7

G6

Port G has the following alternate features:

G7 CKO Oscillator dedicated output or general purpose

input

G6 SI (MICROWIRE Serial Data Input)

G5 SK (MICROWIRE Serial Clock)

G4 SO (MICROWIRE Serial Data Output)

G3 T1A (Timer T1 I/O)

G2 T1B (Timer T1 Capture Input)

G1 WDOUT WATCHDOG and/or CLock Monitor if WATCH-

DOG enabled, otherwise it is a general purpose I/O

G0 INTR (External Interrupt Input)

Port C is an 8-bit I/O port. The 40-pin device does not have

a full complement of Port C pins. The unavailable pins are

not terminated. A read operation on these unterminated pins

will return unpredictable values. The 28 pin device do not

offer Port C. On this device, the associated Port C Data and

Configuration registers should not be used.

Port F is an 8-bit I/O port. The 28--pin device does not have

a full complement of Port F pins. The unavailable pins are

not terminated. A read operation on these unterminated pins

will return unpredictable values.

Port F1–F3 are used for Comparator 1. Port F4–F6 are used

for Comparator 2.

The Port F has the following alternate features:

F6 COMP2OUT (Comparator 2 Output)

F5 COMP2+IN (Comparator 2 Positive Input)

F4 COMP2-IN (Comparator 2 Negative Input)

F3 COMP1OUT (Comparator 1 Output)

F2 COMP1+IN (Comparator 1 Positive Input)

F1 COMP1-IN (Comparator 1 Negative Input)

C

www.national.com

14

相关PDF资料 |

PDF描述 |

|---|---|

| COP8SGR628N9 | 8-Bit CMOS ROM Based and OTP Microcontrollers with 8k to 32k Memory, Two Comparators and USART |

| COP8SGR628Q6 | 8-Bit CMOS ROM Based and OTP Microcontrollers with 8k to 32k Memory, Two Comparators and USART |

| COP8SGR628Q7 | 8-Bit CMOS ROM Based and OTP Microcontrollers with 8k to 32k Memory, Two Comparators and USART |

| COP8SGR728M6 | 8-Bit CMOS ROM Based and OTP Microcontrollers with 8k to 32k Memory, Two Comparators and USART |

| COP8SGR728M7 | 8-Bit CMOS ROM Based and OTP Microcontrollers with 8k to 32k Memory, Two Comparators and USART |

相关代理商/技术参数 |

参数描述 |

|---|---|

| COP8SGR728M7 | 功能描述:8位微控制器 -MCU RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| COP8SGR728M7/NOPB | 功能描述:8位微控制器 -MCU RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| COP8SGR728M8 | 功能描述:8位微控制器 -MCU RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| COP8SGR728M8/NOPB | 功能描述:8位微控制器 -MCU RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| COP8SGR728N8 | 功能描述:8位微控制器 -MCU RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

发布紧急采购,3分钟左右您将得到回复。