- 您现在的位置:买卖IC网 > PDF目录256766 > CV141PAG8 (INTEGRATED DEVICE TECHNOLOGY INC) 141 SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 PDF资料下载

参数资料

| 型号: | CV141PAG8 |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 141 SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 封装: | GREEN, TSSOP-48 |

| 文件页数: | 4/10页 |

| 文件大小: | 81K |

| 代理商: | CV141PAG8 |

COMMERCIALTEMPERATURERANGE

IDTCV141

1-TO-8DIFFERENTIALCLOCKBUFFER

3

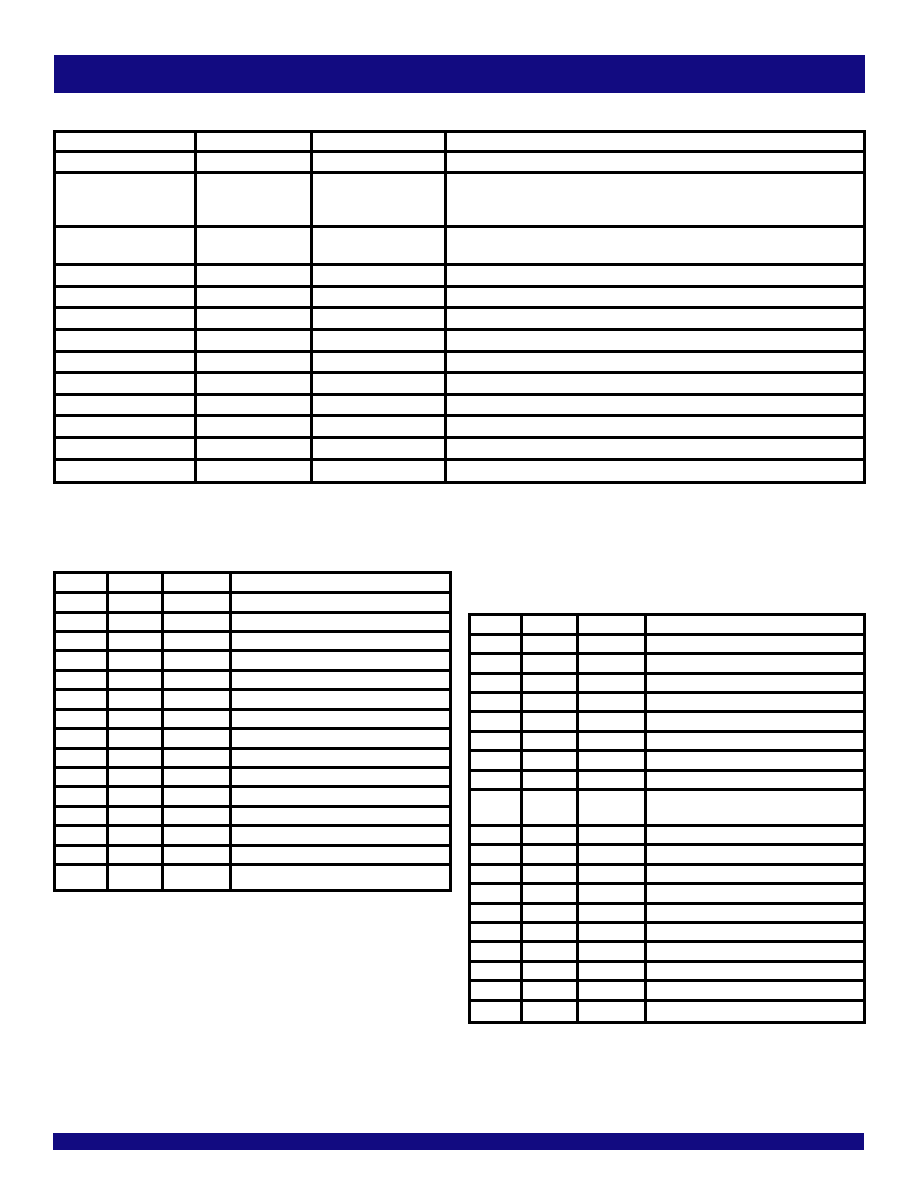

PIN DESCRIPTION

Pin Name

Type

Pin #

Description

SRC_IN, SRC_IN#

IN, DIF

4,5

0.7V differential SRC input

8, 9, 12, 13, 16, 17,

DIF_[7:0], DIF_ [7:0]#

OUT, DIF

20, 21, 29, 30, 33,

0.7Vdifferentialclockoutput

34, 37, 38, 41, 42

OE[7:0]

I N

6, 7, 14, 15,

3.3V LVTTL input for enabling differential outputs (see OE_INV table)

35, 36, 43, 44

PWRDWN

I N

26

3.3V LVTTL for power down (see OE_INV table)

IREF

I N

46

Referencecurrentfordifferentialoutput

LOCK

OUT

45

HIGH, locked

PLL/Bypass#

I N

22

1 = PLL mode, 0 = bypass, PLL OFF

HIGH_BW#

I N

28

0 = HIGH BW, 1 = LOW BW (see HIGH_BW# Selection table)

SRC_DIV2#

I N

1

LOW = divide by 2 mode

SRC_STOP

I N

27

SRC stop (see OE_INV table)

SCL

I N

23

SMBus clock

SDA

I/O, Open Collector

24

SMBus data

OE_INV

I N

40

(see OE_INV table)

INDEX BLOCK WRITE PROTOCOL

Bit

# of bits

From

Description

1

Master

Start

2-9

8

Master

DCh

10

1

Slave

Ack (Acknowledge)

11-18

8

Master

Register offset byte (starting byte)

19

1

Slave

Ack (Acknowledge)

20-27

8

Master

Byte count, N (0 is not valid)

28

1

Slave

Ack (Acknowledge)

29-36

8

Master

first data byte (Offset data byte)

37

1

Slave

Ack (Acknowledge)

38-45

8

Master

2nd data byte

46

1

Slave

Ack (Acknowledge)

:

Master

Nth data byte

Slave

Acknowledge

Master

Stop

INDEX BLOCK READ PROTOCOL

Master can stop reading any time by issuing the stop bit without waiting

until Nth byte (byte count bit30-37).

Bit

# of bits

From

Description

1

Master

Start

2-9

8

Master

DCh

10

1

Slave

Ack (Acknowledge)

11-18

8

Master

Register offset byte (starting byte)

19

1

Slave

Ack (Acknowledge)

20

1

Master

RepeatedStart

21-28

8

Master

DDh

29

1

Slave

Ack (Acknowledge)

30-37

8

Slave

Byte count, N (block read back of N

bytes), power on is 8

38

1

Master

Ack (Acknowledge)

39-46

8

Slave

first data byte (Offset data byte)

47

1

Master

Ack (Acknowledge)

48-55

8

Slave

2nd data byte

Ack (Acknowledge)

:

Master

Ack (Acknowledge)

Slave

Nth data byte

Not acknowledge

Master

Stop

INDEX BYTE WRITE

Setting bit[11:18] = starting address, bit[20:27] = 01h.

INDEX BYTE READ

Setting bit[11:18] = starting address. After reading back the first data byte,

master issues Stop bit.

相关PDF资料 |

PDF描述 |

|---|---|

| C80C52TXXX-20SHXXX:D | 8-BIT, MROM, 20 MHz, MICROCONTROLLER, CDIP40 |

| CT5A1B5C376.800KD12.5 | QUARTZ CRYSTAL RESONATOR, 0.0768 MHz |

| CP24J-12.6MHZ-STBY2-CL | QUARTZ CRYSTAL RESONATOR, 12.6 MHz |

| CSM1-A1B1C1150-29.999D16-3 | QUARTZ CRYSTAL RESONATOR, 29.999 MHz |

| CS10FREQ2HOJ-UB | QUARTZ CRYSTAL RESONATOR, 14 MHz - 50 MHz |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CV142PAG8 | 功能描述:锁相环 - PLL RoHS:否 制造商:Silicon Labs 类型:PLL Clock Multiplier 电路数量:1 最大输入频率:710 MHz 最小输入频率:0.002 MHz 输出频率范围:0.002 MHz to 808 MHz 电源电压-最大:3.63 V 电源电压-最小:1.71 V 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:QFN-36 封装:Tray |

| CV145NLG8 | 制造商:Integrated Device Technology Inc 功能描述: |

| CV146PVG8 | 功能描述:锁相环 - PLL RoHS:否 制造商:Silicon Labs 类型:PLL Clock Multiplier 电路数量:1 最大输入频率:710 MHz 最小输入频率:0.002 MHz 输出频率范围:0.002 MHz to 808 MHz 电源电压-最大:3.63 V 电源电压-最小:1.71 V 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:QFN-36 封装:Tray |

| CV150 | 制造商:KAI SUH SUH ENTERPRISES 功能描述:CABLE TIE 140X3.6 |

| CV-150 | 制造商:KSS 功能描述:Pack |

发布紧急采购,3分钟左右您将得到回复。