- 您现在的位置:买卖IC网 > PDF目录379091 > CY7C374 (Cypress Semiconductor Corp.) UltraLogic 128-Macrocell Flash CPLD(超逻辑的128 宏单元闪速CPLD) PDF资料下载

参数资料

| 型号: | CY7C374 |

| 厂商: | Cypress Semiconductor Corp. |

| 英文描述: | UltraLogic 128-Macrocell Flash CPLD(超逻辑的128 宏单元闪速CPLD) |

| 中文描述: | UltraLogic 128宏单元CPLD的闪光(超逻辑的128个宏单元闪速的CPLD) |

| 文件页数: | 1/1页 |

| 文件大小: | 49K |

| 代理商: | CY7C374 |

For new designs use part CY7C374i

UltraLogic 128-Macrocell Flash CPLD

fax id: 6129

CY7C374

Cypress Semiconductor Corporation

3901 North First Street

San Jose

CA 95134

408-943-2600

September 1992

Revised April 1998

Features

128 macrocells in eight logic blocks

64 I/O pins

6 dedicated inputs including 4 clock pins

Bus Hold capabilities on all I/Os and dedicated inputs

No hidden delays

High speed

—f

MAX

= 100 MHz

—t

PD

= 12 ns

—t

S

= 6 ns

—t

CO

= 7 ns

Electrically Alterable Flash technology

Available in 84-pin PLCC, 84-pin CLCC, 100-pin TQFP,

and 84-pin PGA packages

Pin compatible with the CY7C373

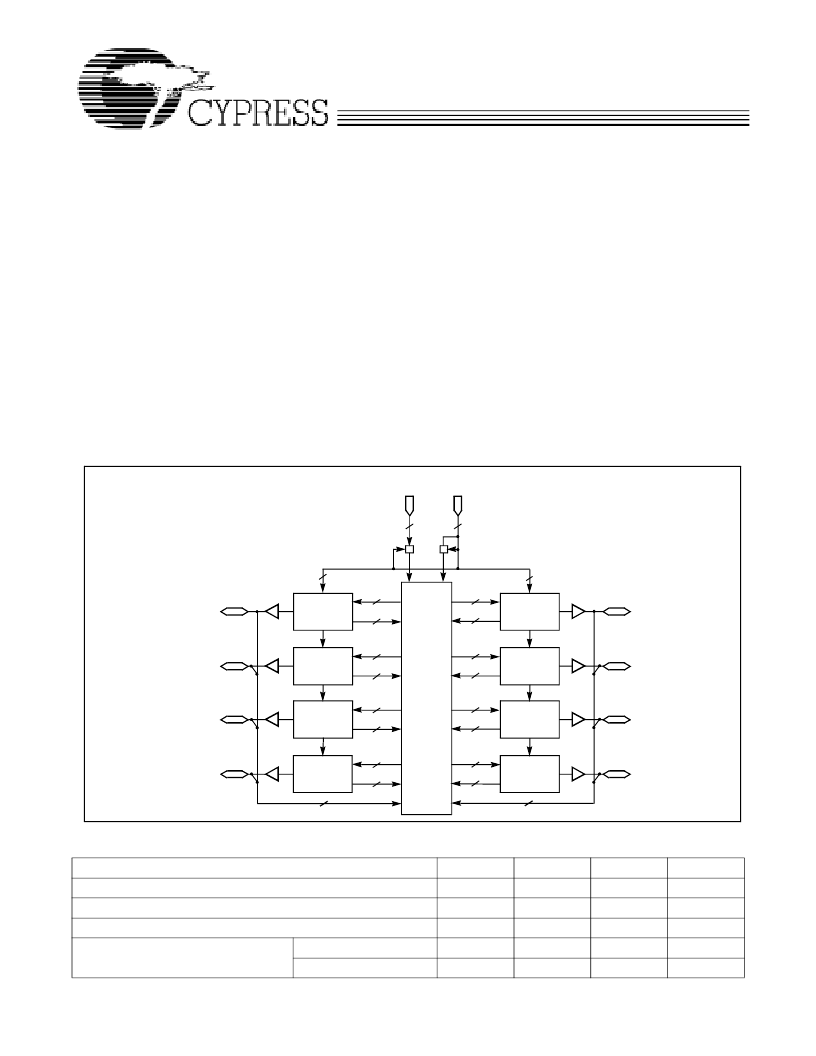

Functional Description

The CY7C374 is a Flash erasable Complex Programmable

Logic Device (CPLD) and is part of the F

LASH

370

family of

high-density, high-speed CPLDs. Like all members of the

F

LASH

370 family, the CY7C374 is designed to bring the ease

of use and high performance of the 22V10 to high-density

CPLDs.

The 128 macrocells in the CY7C374 are divided between eight

logic blocks. Each logic block includes 16 macrocells, a 72 x

86 product term array, and an intelligent product term allocator.

The logic blocks in the F

LASH

370 architecture are connected

with an extremely fast and predictable routing resource—the

Programmable Interconnect Matrix (PIM). The PIM brings flex-

ibility, routability, speed, and a uniform delay to the intercon-

nect.

The CY7C374 is a register intensive 128-Macrocell CPLD. Ev-

ery two macrocells in the device feature an associated I/O pin,

resulting in 64 I/O pins on the CY7C374. In addition, there are

two dedicated inputs and four input/clock pins.

7C374–1

PIM

INPUT

MACROCELLS

CLOCK

INPUTS

INPUTS

LOGIC

BLOCK

B

LOGIC

BLOCK

G

4

4

36

16

16

36

8 I/Os

8 I/Os

LOGIC

BLOCK

A

LOGIC

BLOCK

H

36

16

16

36

8 I/Os

8 I/Os

LOGIC

BLOCK

C

LOGIC

BLOCK

F

36

16

16

36

8 I/Os

8 I/Os

BLOCK

E

LOGIC

36

16

16

36

8 I/Os

8 I/Os

32

32

4

2

INPUT/CLOCK

MACROCELLS

Logic Block Diagram

I/O

0

I/O

7

I/O

8

I/O

15

I/O

16

I/O

23

I/O

24

I/O

31

I/O

56

I/O

63

I/O

48

I/O

55

I/O

40

I/O

47

I/O

32

I/O

39

LOGIC

BLOCK

D

Selection Guide

7C374-100

7C374-83

7C374-66

7C374L-66

Maximum Propagation Delay t

PD

(ns)

Minimum Set-Up, t

S

(ns)

Maximum Clock to Output, t

CO

(ncs)

Maximum Supply

Current, I

CC

(mA)

12

15

20

20

6

8

10

10

7

8

10

10

Commercial

300

300

300

150

Military/Industrial

370

370

相关PDF资料 |

PDF描述 |

|---|---|

| CY7C375i | UltraLogic 128-Macrocell Flash CPLD(超逻辑的128-宏单元闪速CPLD) |

| CY7C375 | UltraLogic 128-Macrocell Flash CPLD(超逻辑的128 宏单元闪速CPLD) |

| CY7C402 | 64 x 5 Cascadable FIFO(64 x 5位级联型先进先出(FIFO)) |

| CY7C401 | 64 x 4 Cascadable FIFO(64 x 4 位级联型先进先出(FIFO)) |

| CY7C403 | 64 x 4 Cascadable FIFO(64 x 4 位级联型先进先出(FIFO)) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CY7C3741-125JC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CY7C3741-66JC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C374I100AC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C374I-100AC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C374I-100JC | 制造商:Cypress Semiconductor 功能描述:CPLD FLASH370i Family 3.2K Gates 128 Macro Cells 5V 84-Pin PLCC |

发布紧急采购,3分钟左右您将得到回复。