- 您现在的位置:买卖IC网 > PDF目录9359 > DS1501YZ+T&R (Maxim Integrated Products)IC RTC WDOG Y2KC 5.0V 28-SOIC PDF资料下载

参数资料

| 型号: | DS1501YZ+T&R |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 7/22页 |

| 文件大小: | 0K |

| 描述: | IC RTC WDOG Y2KC 5.0V 28-SOIC |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 1,000 |

| 类型: | 时钟/日历 |

| 特点: | 警报器,闰年,NVSRAM,方波输出,监视计时器,Y2K |

| 存储容量: | 256B |

| 时间格式: | HH:MM:SS(24 小时) |

| 数据格式: | YY-MM-DD-dd |

| 接口: | 并联 |

| 电源电压: | 4.5 V ~ 5.5 V |

| 电压 - 电源,电池: | 2.5 V ~ 3.7 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-SOIC(0.295",7.50mm 宽) |

| 供应商设备封装: | 28-SOIC W |

| 包装: | 带卷 (TR) |

DS1501/DS1511 Y2KC Watchdog Real-Time Clocks

15 of 22

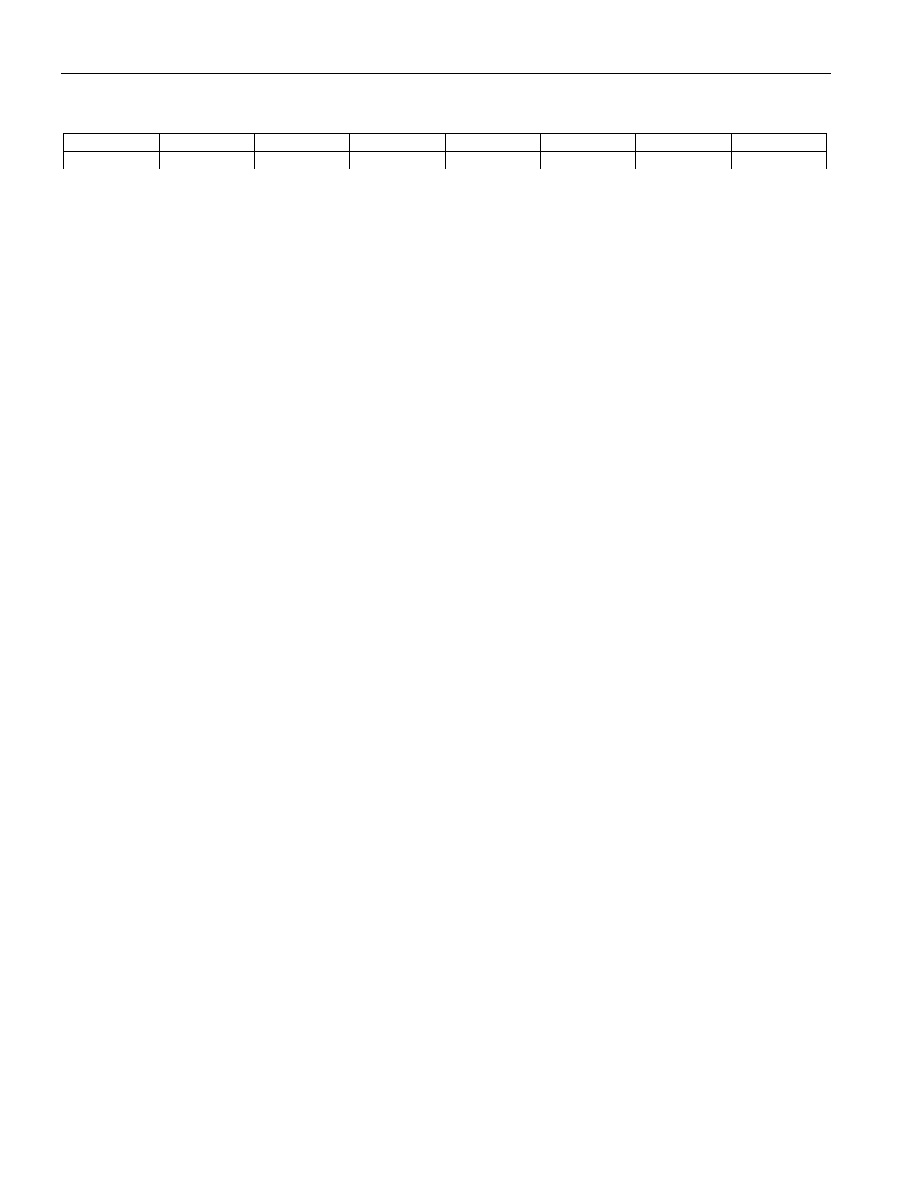

Control A Register (0Eh)

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

BLF1

BLF2

PRS

PAB

TDF

KSF

WDF

IRQF

BLF1, Valid RAM and Time Bit 1 (0Eh Bit 7); BLF2, Valid RAM and Time Bit 2 (0Eh Bit 6)

These status bits give the condition of any batteries attached to the VBAT or VBAUX pins. The DS1501/DS1511

constantly monitor the battery voltage of the backup-battery sources (VBAT and VBAUX). The BLF1 and BLF2 bits are

set to 1 if the battery voltages on VBAT and VBAUX are less than VBLF (typ), otherwise BLF1 and BLF2 bits are 0.

BLF1 reflects the condition of VBAT with BLF2 reflecting VBAUX. If either bit is read as 1, the voltage on the respective

pin is inadequate to maintain the RAM memory or clock functions. These bits are read only.

PRS, Reset Select Bit (0Eh Bit 5)

When set to 0, the PWR pin is set high-Z when the DS1501/DS1511 go into power-fail. When set to 1, the PWR pin

remains active upon entering power-fail.

PAB, Power Active-Bar Control Bit (0Eh Bit 4)

When this bit is 0, the PWR pin is in the active-low state. When this bit is 1, the PWR pin is in the high-impedance

state. The user can write this bit to 1 or 0. If either TDF and TPE = 1 or KSF = 1, the PAB bit is cleared to 0. This bit

can be read or written.

TDF, Time-of-Day/Date Alarm Flag (0Eh Bit 3)

A 1 in the TDF bit indicates that the current time has matched the alarm time. If the TIE bit is also 1, the IRQ pin

goes low and a 1 appears in the IRQF bit. This bit is cleared by reading the register or writing it to 0.

KSF, Kickstart Flag (0Eh Bit 2)

This bit is set to a 1 when a kickstart condition occurs or when the user writes it to 1. If the KIE bit is also 1, the IRQ

pin goes low and a 1 appears in the IRQF bit. This bit is cleared by reading the register or writing it to 0.

WDF, Watchdog Flag (0Eh Bit 1)

If the processor does not access the DS1501/DS1511 with a write within the period specified in addresses 0Ch and

0Dh, the WDF bit is set to 1. WDF is cleared by writing it to 0.

IRQF, Interrupt Request Flag (0Eh Bit 0)

The interrupt request flag (IRQF) bit is set to 1 when one or more of the following are true:

TDF = TIE = 1

KSF = KIE = 1

WDF = WDE = 1

i.e., IRQF = (TDF x TIE) + (KSF x KIE) + (WDF x WDE)

Any time the IRQF bit is 1, the IRQ pin is driven low.

Clearing IRQ and Flags

The time-of-day/date alarm flag (TDF), watchdog flag (WDF), kickstart flag (KSF), and interrupt request flag (IRQF)

are cleared by reading the flag register (0Eh). The address must be stable for a minimum of 15ns while CE and OE

are active. After the address stable requirement has been met, either a change in address, a rising edge of OE, or

a rising edge of CE causes the flags to be cleared. The IRQ pin goes inactive after the IRQF flag is cleared. TDF

and WDF can also be cleared by writing to 0.

相关PDF资料 |

PDF描述 |

|---|---|

| DS1845E-050+ | IC POT/MEM DUAL NV 50K 14-TSSOP |

| DS1340C-3# | IC RTC I2C W/CHARGER 16-SOIC |

| DS1340C-18# | IC RTC I2C W/CHARGER 16-SOIC |

| MAX5489EUD+ | IC DGTL POT DUAL 256-TAP 14TSSOP |

| DS1338C-18# | IC RTC 56BIT NV SRAM 16-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS1503MRAB0 | 制造商:Thomas & Betts 功能描述:100A,REC,4P5W,MG,503,AB0,220V,SC |

| DS1504FP00K | 制造商:Thomas & Betts 功能描述:100A,CON,4P5W,MG,504,00K,3PY277V |

| DS1504FP00K/DF1026 | 制造商:Thomas & Betts 功能描述:100A,CON,4P5W,MG,504,00K,3PY277V |

| DS1504FR000 | 制造商:Thomas & Betts 功能描述:100A,REC,4P5W,MG,504,3PY277V |

| DS1504FR00K | 制造商:Thomas & Betts 功能描述:100A,REC,4P5W,MG,504,00K,3PY277,SC |

发布紧急采购,3分钟左右您将得到回复。