- 您现在的位置:买卖IC网 > PDF目录299030 > EP20K100BI196-1 (ALTERA CORP) LOADABLE PLD, PBGA196 PDF资料下载

参数资料

| 型号: | EP20K100BI196-1 |

| 厂商: | ALTERA CORP |

| 元件分类: | PLD |

| 英文描述: | LOADABLE PLD, PBGA196 |

| 文件页数: | 12/68页 |

| 文件大小: | 975K |

| 代理商: | EP20K100BI196-1 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页当前第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页

2

Altera Corporation

APEX 20K Programmable Logic Device Family Data Sheet

Preliminary Information

...and More

Features

s

Designed for low-power operation

–

1.8-V and 2.5-V supply voltage (see Table 2)

–

MultiVoltTM I/O interface support to interface with 1.8-V, 2.5-V,

and 3.3-V devices (see Table 2)

–

ESB offering programmable power-saving mode

s

Flexible clock management circuitry with phase-locked loop (PLL)

–

Built-in low-skew clock tree

–

Up to eight global clock signals

–

ClockLockTM feature reducing clock delay and skew

–

ClockBoostTM feature providing clock multiplication

–

ClockShiftTM programmable clock phase and delay shifting

s

Powerful I/O features

–

Compliant with peripheral component interconnect Special

Interest Group (PCI SIG) PCI Local Bus Specification,

Revision 2.2

for 3.3-V operation at 33 or 66 MHz and 32 or 64 bits

–

Bidirectional I/O performance (tCO + tSU) up to 243 MHz

–

Direct connection from I/O pins to local interconnect providing

fast tCO and tSU times for complex logic

–

MultiVolt I/O interface support to interface with 1.8-V, 2.5-V,

and 3.3-V devices (see Table 2)

–

Programmable clamp to VCCIO

–

Individual tri-state output enable control for each pin

–

Programmable output slew-rate control to reduce switching

noise

–

Support for advanced I/O standards, including low-voltage

differential signaling (LVDS), stub-series terminated logic

(SSTL-3), and Gunning transceiver logic (GTL+)

–

Supports hot-socketing operation

–

Pull-up on I/O pins before and during configuration

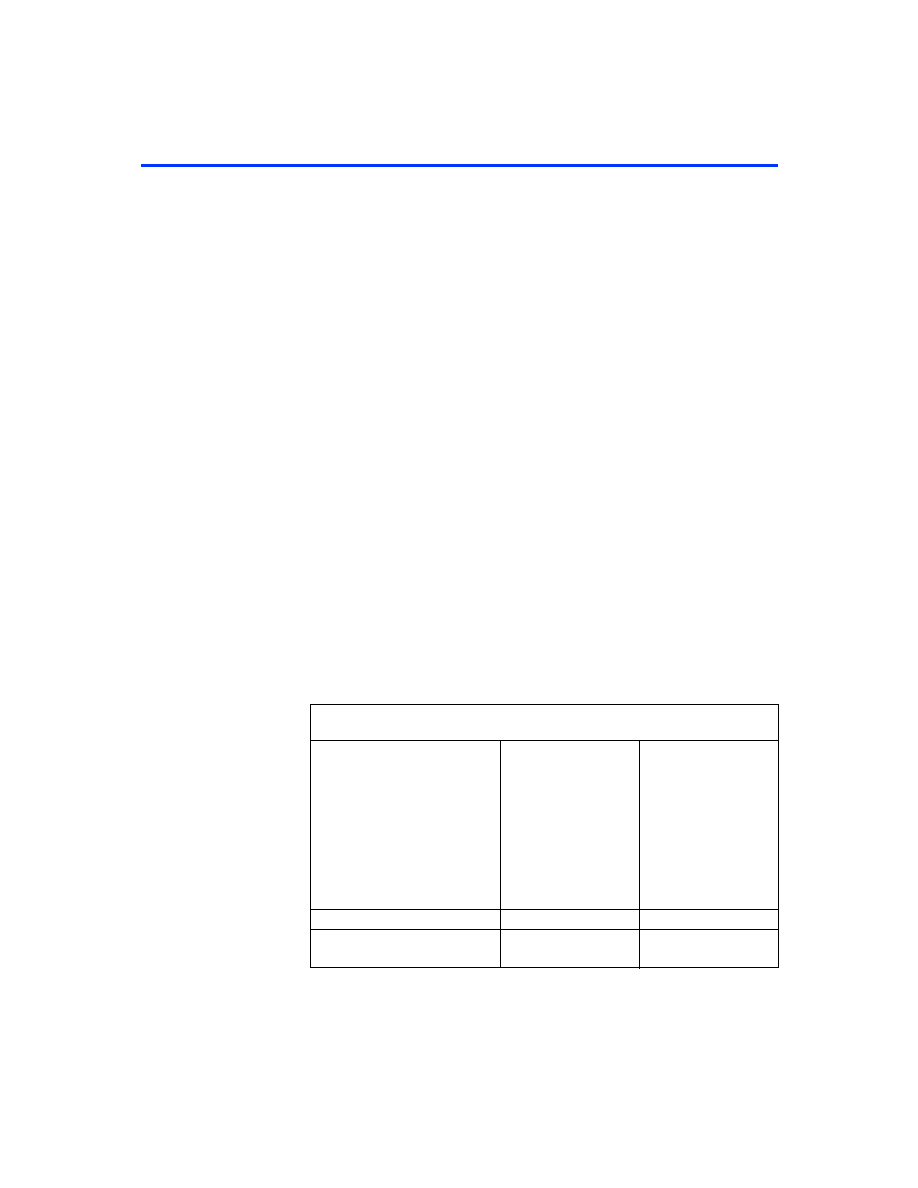

Table 2. APEX 20K Supply Voltages

Feature

EP20K100

EP20K200

EP20K400

EP20K60E

EP20K100E

EP20K160E

EP20K200E

EP20K300E

EP20K400E

EP20K600E

EP20K1000E

EP20K1500E

Internal supply voltage (VCCINT)

2.5 V

1.8 V

MultiVolt I/O interface voltage

levels (VCCIO)

2.5 V, 3.3 V

1.8 V, 2.5 V, 3.3 V

相关PDF资料 |

PDF描述 |

|---|---|

| EP20K100BI196-2 | LOADABLE PLD, PBGA196 |

| EP20K100BI196-3 | LOADABLE PLD, PBGA196 |

| EP20K100BC324-1 | LOADABLE PLD, PBGA324 |

| EP20K100BC324-2 | LOADABLE PLD, PBGA324 |

| EP20K100BC324-3 | LOADABLE PLD, PBGA324 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EP20K100BI356-1 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

| EP20K100BI356-1ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

| EP20K100BI356-2 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

| EP20K100BI356-2ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

| EP20K100BI356-3 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

发布紧急采购,3分钟左右您将得到回复。