- 您现在的位置:买卖IC网 > PDF目录43999 > LK1501-9ERD1T 1-OUTPUT 150 W AC-DC REG PWR SUPPLY MODULE PDF资料下载

参数资料

| 型号: | LK1501-9ERD1T |

| 元件分类: | 电源模块 |

| 英文描述: | 1-OUTPUT 150 W AC-DC REG PWR SUPPLY MODULE |

| 封装: | HEAT SINK, METAL, CASE K02, MODULE |

| 文件页数: | 14/27页 |

| 文件大小: | 640K |

| 代理商: | LK1501-9ERD1T |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页

K-Family

DC-DC Converters >100 W

Rugged Environment

8 - 22

Edition 2/96 - Melcher AG

MELCHER

The Power Partners.

8.1

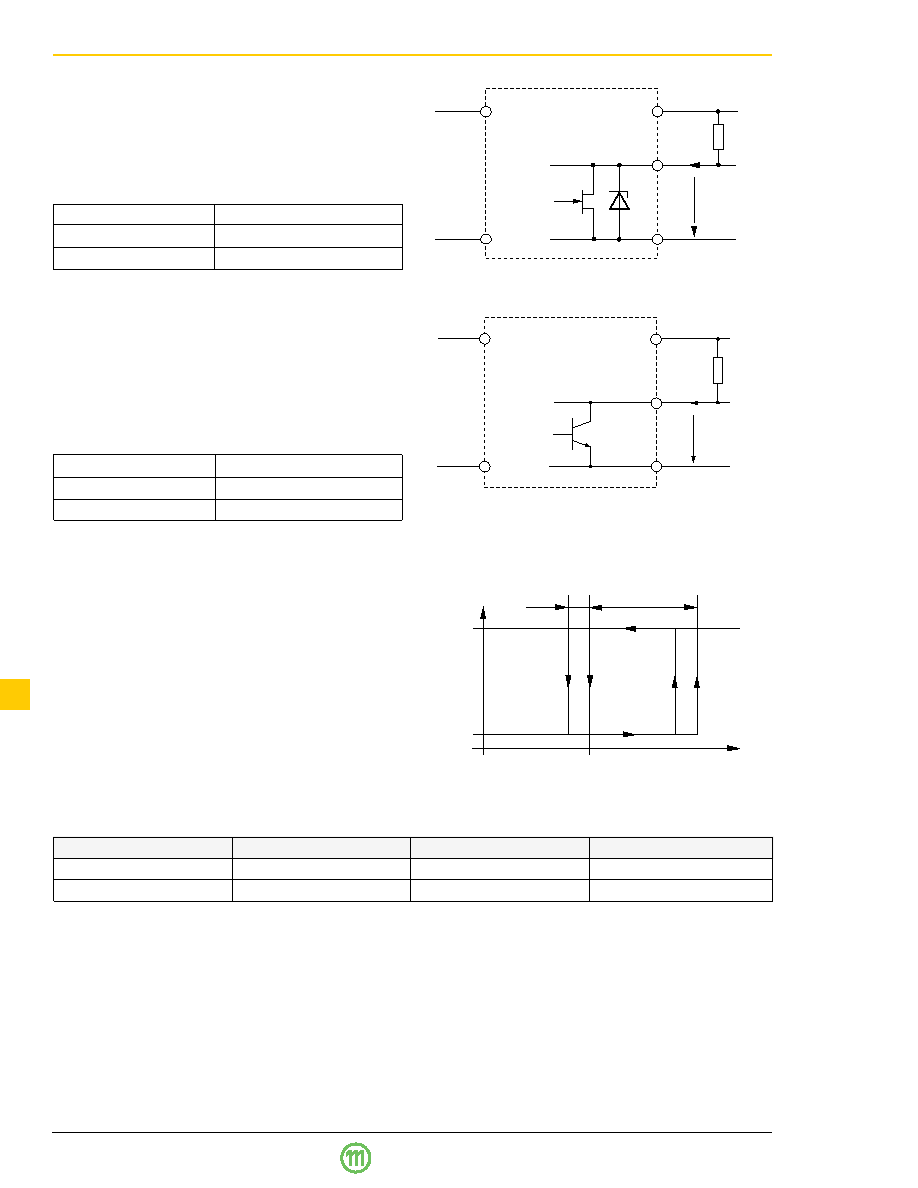

Fig. 24

Option D1...D0: JFET output, ID ≤ 2.5 mA

NPN output (D5...DD):

Connector pin D is internally connected via the collector-

emitter path of a NPN transistor to the negative potential of

output 1.

UD < 0.4 V (logic low) corresponds to a monitored

voltage level (

Ui and/or Uo1) > Ut +Uh. The current ID

through the open collector should not exceed 20 mA. The

NPN output is not protected against external overvoltages.

UD should not exceed 40 V.

Ui, Uo1 status

D output,

UD

Ui or Uo1 < Ut

high, H,

I D ≤ 25 A at UD = 40 V

Ui and Uo1 > Ut + Uh

low, L,

UD

≤ 0.4 V at ID = 20 mA

Threshold tolerances and hysteresis:

If

Ui is monitored, the internal input voltage after the input

filter and rectifier (LK types) is measured. Consequently

this voltage differs from the voltage at the connector pins by

the voltage drop

U

ti across input filter and rectifier. The

threshold levels of the D0 and D9 options are factory ad-

justed at nominal output current

Io nom and at TA = 25 °C. The

value of

U

ti depends upon the input voltage range (CK,

DK, ..), threshold level

Ut, temperature and input current.

The input current is a function of the input voltage and the

output power.

Fig. 26

Definition of Uti, Ut i and Uhi (JFET output)

Table 16: D-output logic signals

Version of D

Ui < Ut resp. Uo < Ut

Ui > Ut + Uh resp. Uo > Ut

Configuration

D1, D2, D3, D4, D0

low

high

JFET

D5, D6, D7, D8, D9, DD

high

low

NPN

JFET output (D0…D4):

Connector pin D is internally connected via the drain-

source path of a JFET (self-conducting type) to the nega-

tive potential of output 1.

UD ≤ 0.4 V (logic low) corresponds

to a monitored voltage level (

Ui and/or Uo1) < Ut. The cur-

rent

ID through the JFET should not exceed 2.5 mA. The

JFET is protected by a 0.5 W Zener diode of 8.2 V against

external overvoltages.

Ui, Uo1 status

D output,

UD

Ui or Uo1 < Ut

low, L,

UD ≤ 0.4 V at ID = 2.5 mA

Ui and Uo1 > Ut + Uh

high, H,

ID

≤ 25 A at UD = 5.25 V

Vo1+

Vo1–

D

UD

ID

Vi+

Vi–

Rp

U

ti

U

hi

U

D low

U

D

U

D high

U

i

P

o

=

P

o

nom

P

o

=

0

P

o

=

0

U

ti

P

o

=

P

o

nom

Vo1+

Vo1–

D

UD ≤ 6 V

ID

Vi+

Vi–

Rp

Fig. 25

Option D5...DD: NPN output, Uo1 ≤ 40 V, ID ≤ 20 mA

相关PDF资料 |

PDF描述 |

|---|---|

| LK1501-9RD8TB1 | 1-OUTPUT 150 W AC-DC REG PWR SUPPLY MODULE |

| LK1601-9EPD0B1 | 1-OUTPUT 150 W AC-DC REG PWR SUPPLY MODULE |

| LK1601-9EPD2B1 | 1-OUTPUT 150 W AC-DC REG PWR SUPPLY MODULE |

| LK1601-9RD3T | 1-OUTPUT 150 W AC-DC REG PWR SUPPLY MODULE |

| LK1601-9RD6TB1 | 1-OUTPUT 150 W AC-DC REG PWR SUPPLY MODULE |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EPM3512AQC208-10 | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD - MAX 3000A 512 Macro 172 IOs RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| EPM3512AQC208-10N | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD - MAX 3000A 512 Macro 172 IOs RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| EPM3512AQC208-7 | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD - MAX 3000A 512 Macro 172 IOs RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| EPM3512AQC208-7N | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD - MAX 3000A 512 Macro 172 IOs RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| EPM3512AQI208-10 | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD - MAX 3000A 512 Macro 172 IOs RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

发布紧急采购,3分钟左右您将得到回复。