- 您现在的位置:买卖IC网 > PDF目录67682 > IBM25PPC405GP-3EE266C 32-BIT, 266.66 MHz, RISC PROCESSOR, PBGA413 PDF资料下载

参数资料

| 型号: | IBM25PPC405GP-3EE266C |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 266.66 MHz, RISC PROCESSOR, PBGA413 |

| 封装: | 25 X 25 MM, ENHANCED, PLASTIC, BGA-413 |

| 文件页数: | 44/60页 |

| 文件大小: | 1480K |

| 代理商: | IBM25PPC405GP-3EE266C |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页当前第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页

PowerPC 405GP Embedded Processor Data Sheet

6/20/03

Page 49 of 60

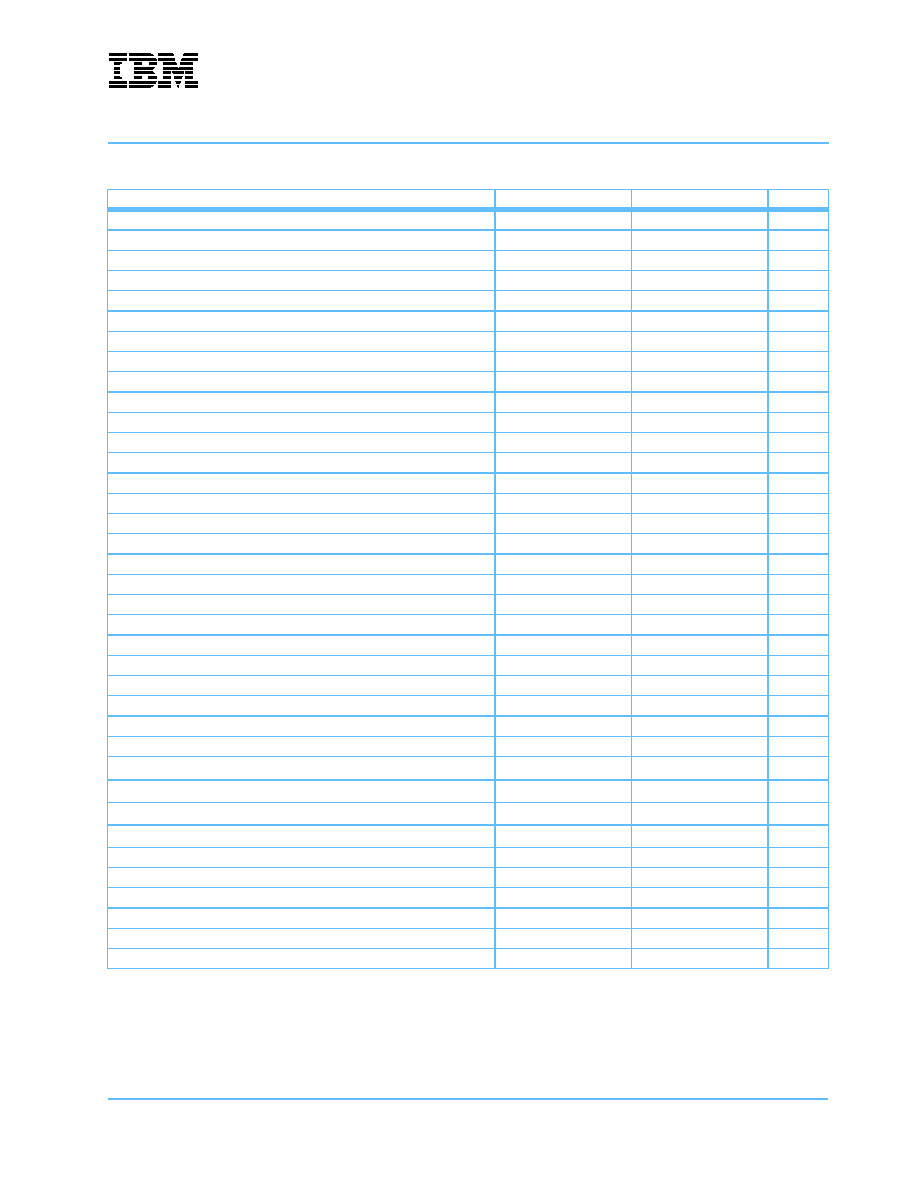

Peripheral Interface Clock Timings

Parameter

Min

Max

Units

PCIClk input frequency (asynchronous mode)

Note 1

66.66

MHz

PCIClk period (asynchronous mode)

15

Note 1

ns

PCI Clock frequency (synchronous mode)

25

33.33

MHz

PCI Clock period (synchronous mode - Note 2)

30

40

ns

PCIClk input high time

40% of nominal period

60% of nominal period

ns

PCIClk input low time

40% of nominal period

60% of nominal period

ns

EMCMDClk output frequency

–

2.5

MHz

EMCMDClk period

400

–

ns

EMCMDClk output high time

160

–

ns

EMCMDClk output low time

160

–

ns

PHYTxClk input frequency

2.5

25

MHz

PHYTxClk period

40

400

ns

PHYTxClk input high time

35% of nominal period

–

ns

PHYTxClk input low time

35% of nominal period

–

ns

PHYRxClk input frequency

2.5

25

MHz

PHYRxClk period

40

400

ns

PHYRxClk input high time

35% of nominal period

–

ns

PHYRxClk input low time

35% of nominal period

–

ns

PerClk output frequency–133MHz

–

33.33

MHz

PerClk period–133MHz

30

–

ns

PerClk output frequency–200MHz

–

50

MHz

PerClk period–200MHz

20

–

ns

PerClk output frequency–266MHz

–

66.66

MHz

PerClk period–266MHz

15

–

ns

PerClk output high time

45% of nominal period

55% of nominal period

ns

PerClk output low time

45% of nominal period

55% of nominal period

ns

PerClk clock edge stability (phase jitter, cycle to cycle)

± 0.3

ns

UARTSerClk input frequency (Note 3)

–

1000/(2TOPB+2ns)

MHz

UARTSerClk period

2TOPB+2

–ns

UARTSerClk input high time

TOPB+1

–ns

UARTSerClk input low time

TOPB+1

–ns

TmrClk input frequency–133MHz

–

33.33

MHz

TmrClk period–133 MHz

30

–

ns

TmrClk input frequency–200MHz

–

50

MHz

TmrClk period–200 MHz

20

–

ns

TmrClk input frequency–266MHz

–

66.66

MHz

TmrClk period–266 MHz

15

–

ns

相关PDF资料 |

PDF描述 |

|---|---|

| IBM25PPC405GP-3DE266CZ | 32-BIT, 266.66 MHz, RISC PROCESSOR, PBGA456 |

| IBM25PPC405GP-3BE133C | 32-BIT, 133.33 MHz, RISC PROCESSOR, PBGA456 |

| IBM25PPC405GPR-3BA333CZ | 32-BIT, 333 MHz, RISC PROCESSOR, PBGA456 |

| IBM25PPC405GPR3DB400Z | 32-BIT, 400 MHz, RISC PROCESSOR, PBGA456 |

| IBM25PPC405GPR3BB400Z | 32-BIT, 400 MHz, RISC PROCESSOR, PBGA456 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IBM25PPC405GP3EE266CZ | 制造商:IBM 功能描述: |

| IBM25PPC405GPR3BB266 | 制造商:IBM 功能描述: |

| IBM25PPC405-GPR-3JB266Z | 制造商:IBM 功能描述: |

| IBM25PPC405GPR-3KB266C | 制造商:IBM 功能描述: |

| IBM25PPC440GX3CB667C | 制造商:IBM 功能描述: |

发布紧急采购,3分钟左右您将得到回复。