- 您现在的位置:买卖IC网 > PDF目录10010 > IDT723616L20PF (IDT, Integrated Device Technology Inc)IC FIFO TRPL BUS 64X36X2 128QFP PDF资料下载

参数资料

| 型号: | IDT723616L20PF |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 16/26页 |

| 文件大小: | 0K |

| 描述: | IC FIFO TRPL BUS 64X36X2 128QFP |

| 标准包装: | 72 |

| 系列: | 7200 |

| 功能: | 同步 |

| 存储容量: | 4.6K(64 x 36 x2) |

| 数据速率: | 50MHz |

| 访问时间: | 20ns |

| 电源电压: | 4.5 V ~ 5.5 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 128-LQFP |

| 供应商设备封装: | 128-TQFP(14x20) |

| 包装: | 托盘 |

| 其它名称: | 723616L20PF |

23

COMMERCIALANDINDUSTRIAL

TEMPERATURERANGES

IDT723616 CMOS TRIPLE BUS SyncFIFO

WITH

BUS-MATCHING AND BYTE SWAPPING 64 x 36 x 2

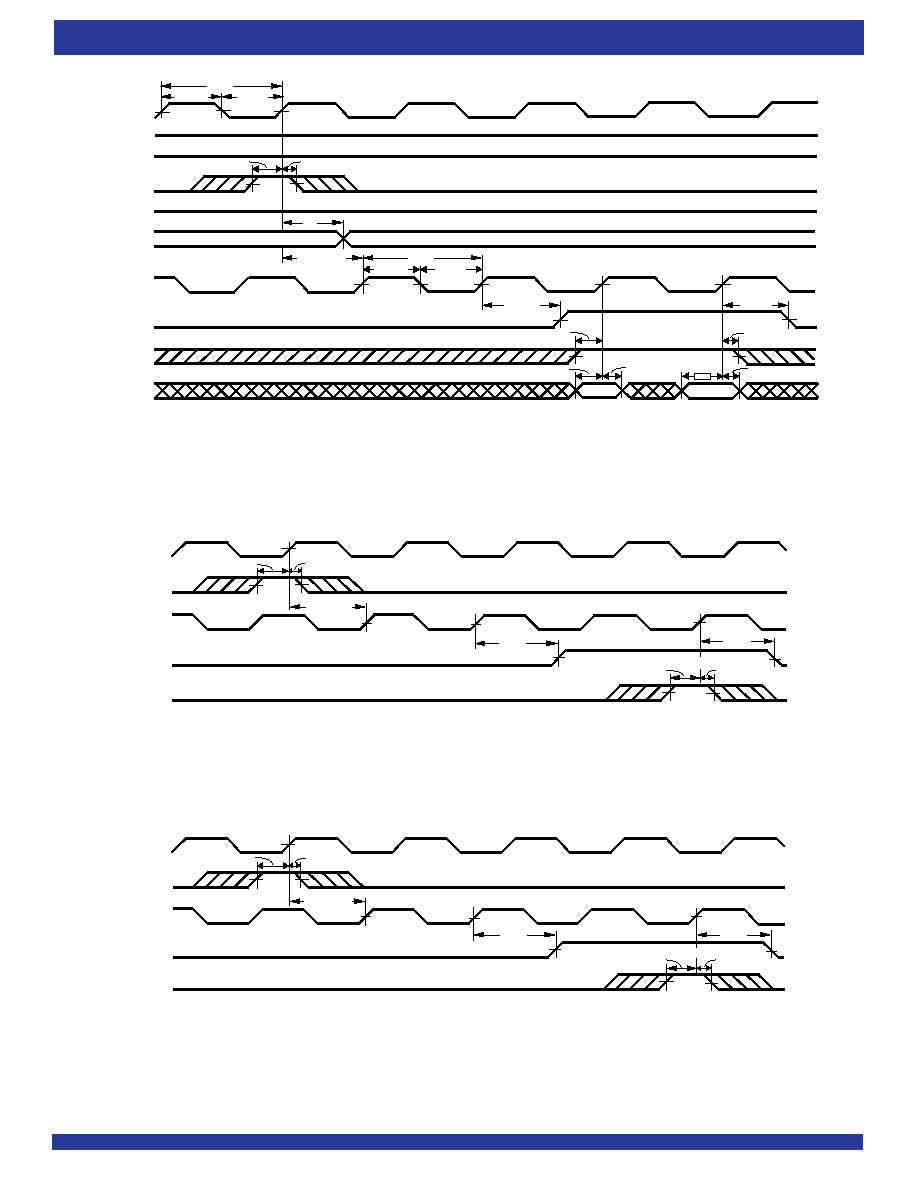

AEB

CLKA

RENB

3520 drw16

ENA

CLKB

2

1

tENS

tENH

tSKEW2

tPAE

tENS

tENH

X Long Word in FIFO1

(X+1) Long Words in FIFO1

(1)

NOTES:

1. tSKEW2 is the minimum time between a rising CLKA edge and a rising CLKB edge for

AEB to transition HIGH in the next CLKB cycle. If the time between the rising CLKA

edge and rising CLKB edge is less than tSKEW2, then

AEB may transition HIGH one CLKB cycle later than shown.

2. FIFO1 Write (

CSA = LOW, W/RA = HIGH).

3. Port-B size is word or byte;

AEB is set LOW by the last word or byte read of the long word, respectively.

Figure 16. Timing for AEB when FIFO1 is Almost-Empty

Figure 17. Timing for

AEA

AEA when FIFO2 is Almost-Empty

AEA

CLKC

ENA

3520 drw17

WENC

CLKA

2

1

tENS

tENH

tSKEW2

tPAE

tENS

tENH

(X+1) Long Words in FIFO2

X Long Words in FIFO2

(1)

NOTES:

1. tSKEW2 is the minimum time between a rising CLKC edge and a rising CLKA edge for

AEA to transition HIGH in the next CLKA cycle. If the time between the rising CLKC edge

and rising CLKA edge is less than tSKEW2, then

AEA may transition HIGH one CLKA cycle later than shown.

2. FIFO2 read (

CSA = LOW, W/RA = LOW).

3. Port-C size is word or byte; tSKEW2 is referenced from the rising CLKC edge that writes the last word or byte of the long word, respectively.

CSA

EFA

ENA

A0 - A35

CLKA

FFC

CLKC

3520 drw15

12

C0 - C17

WENC

tCLK

tCLKH

tCLKL

tENS

tENH

tA

tSKEW1

tCLK

tCLKH

tCLKL

tENS

tDS

tENH

tDH

To FIFO2

Previous Word in FIFO2 Output Register

Next Word From FIFO2

LOW

W/RA LOW

HIGH

(1)

FIFO2 Full

tWFF

tDH

tDS

Figure 15.

FFC

FFC Flag Timing and First Available Write when FIFO2 is Full

NOTES:

1. tSKEW1 is the minimum time between a rising CLKA edge and a rising CLKB edge for

FFB to transition HIGH in the next CLKB cycle. If the time between the rising CLKA edge

and rising CLKB edge is less than tSKEW1, then

FFB may transition HIGH one CLKB cycle later than shown.

2. Port-C size is word or byte;

FFC is set LOW by the last word or byte write of the long word, respectively. (The word-size case is shown.)

相关PDF资料 |

PDF描述 |

|---|---|

| LTC2845IUHF | IC TXRX 3.3V MULTIPROTOCOL 38QFN |

| IDT72V831L15PFI8 | IC SYNC FIFO 2048X9 15NS 64QFP |

| AD7306AR-REEL | IC TXRX RS-232 RS-422 24-SOIC |

| VE-BNK-MX-B1 | CONVERTER MOD DC/DC 40V 75W |

| VE-BNJ-MX-B1 | CONVERTER MOD DC/DC 36V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT723616L20PF8 | 功能描述:IC FIFO TRPL BUS 64X36X2 128QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:7200 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT723616L20PFI | 功能描述:IC FIFO TRPL BUS 64X36X2 128QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:7200 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT723616L20PFI8 | 功能描述:IC FIFO TRPL BUS 64X36X2 128QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:7200 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT723622L12PF | 功能描述:IC FIFO SYNC 256X36X2 120QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:7200 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT723622L12PF8 | 功能描述:IC FIFO SYNC 256X36X2 120QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:7200 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

发布紧急采购,3分钟左右您将得到回复。