- 您现在的位置:买卖IC网 > PDF目录10011 > IDT72V3631L15PF8 (IDT, Integrated Device Technology Inc)IC SYNCFIFO 512X36 15NS 120-TQFP PDF资料下载

参数资料

| 型号: | IDT72V3631L15PF8 |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 2/21页 |

| 文件大小: | 0K |

| 描述: | IC SYNCFIFO 512X36 15NS 120-TQFP |

| 标准包装: | 750 |

| 系列: | 72V |

| 功能: | 异步,同步 |

| 存储容量: | 18.4K(512 x 36) |

| 数据速率: | 67MHz |

| 访问时间: | 15ns |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 120-LQFP |

| 供应商设备封装: | 120-TQFP(14x14) |

| 包装: | 带卷 (TR) |

| 其它名称: | 72V3631L15PF8 |

10

COMMERCIALTEMPERATURERANGE

IDT72V3631/72V3641/72V3651

3.3V CMOS SYNCFIFO 512 x 36, 1,024 x 36 and 2,048 x 36

SYNCHRONIZED FIFO FLAGS

Each IDT72V3631/72V3641/72V3651 FIFO flag is synchronized to its port

Clock through at least two flip-flop stages. This is done to improve the flags’

reliabilitybyreducingtheprobabilityofmetastableeventsontheiroutputswhen

CLKA and CLKB operate asynchronously to one another. OR and

AE are

synchronized to CLKB. IR and

AF aresynchronizedtoCLKA. Table4shows

the relationship of each flag to the number of words stored in memory.

OUTPUT READY FLAG (OR)

TheOutputReadyflagofaFIFOissynchronizedtotheportClockthatreads

data from its array (CLKB). When the OR flag is HIGH, new data is present

in the FIFO output register. When the OR flag is LOW, the previous data word

is present in the FIFO output register and attempted FIFO reads are ignored.

A FIFO read pointer is incremented each time a new word is clocked to its

output register. The state machine that controls an OR flag monitors a write-

pointer and read-pointer comparator that indicates when the FIFO memory

statusisempty,empty+1,orempty+2. FromthetimeawordiswrittentoaFIFO,

itcanbeshiftedtotheFIFOoutputregisterinaminimumofthreecyclesofCLKB.

Therefore, an OR flag is LOW if a word in memory is the next data to be sent

to the FIFO output register and three CLKB cycles have not elapsed since the

time the word was written. The OR flag of the FIFO remains LOW until the third

LOW-to-HIGH transition of CLKB occurs, simultaneously forcing the OR flag

HIGH and shifting the word to the FIFO output register.

ALOW-to-HIGHtransitiononCLKBbeginsthefirstsynchronizationcycleof

a write if the clock transition occurs at time tSKEW1 or greater after the write.

Otherwise, the subsequent CLKB cycle may be the first synchronization cycle

(see Figure 7).

INPUT READY FLAG (IR)

The Input Ready flag of a FIFO is synchronized to the port Clock that writes

data to its array (CLKA). When the IR flag is HIGH, a memory location is free

in the FIFO to write new data. No memory locations are free when the IR flag

is LOW and attempted writes to the FIFO are ignored.

Each time a word is written to a FIFO, its write pointer is incremented. The

state machine that controls an IR flag monitors a write-pointer and read pointer

comparator that indicates when the FIFO memory status is full, full-1, or full-2.

FromthetimeawordisreadfromaFIFO,itspreviousmemorylocationisready

tobewritteninaminimumofthreecyclesofCLKA. Therefore,anIRflagisLOW

iflessthantwocyclesofCLKAhaveelapsedsincethenextmemorywritelocation

has been read. The second LOW-to-HIGH transition on CLKA after the read

sets the Input Ready flag HIGH, and data can be written in the following cycle.

ALOW-to-HIGHtransitiononCLKAbeginsthefirstsynchronizationcycleof

a read if the clock transition occurs at time tSKEW1 or greater after the read.

Otherwise, the subsequent CLKA cycle may be the first synchronization cycle

(see Figure 8).

ALMOST-EMPTY FLAG (

AE)

TheAlmost-EmptyflagofaFIFOissynchronizedtotheportClockthatreads

datafromitsarray(CLKB). Thestatemachinethatcontrolsan

AEflagmonitors

a write-pointer and read-pointer comparator that indicates when the FIFO

memory status is almost-empty, almost-empty+1, or almost-empty+2. The

almost-emptystateisdefinedbythecontentsofregisterX. Thisregisterisloaded

with a preset value during a FIFO reset, programmed from port A, or

programmed serially (see Almost-Empty flag and Almost-Full flag offset pro-

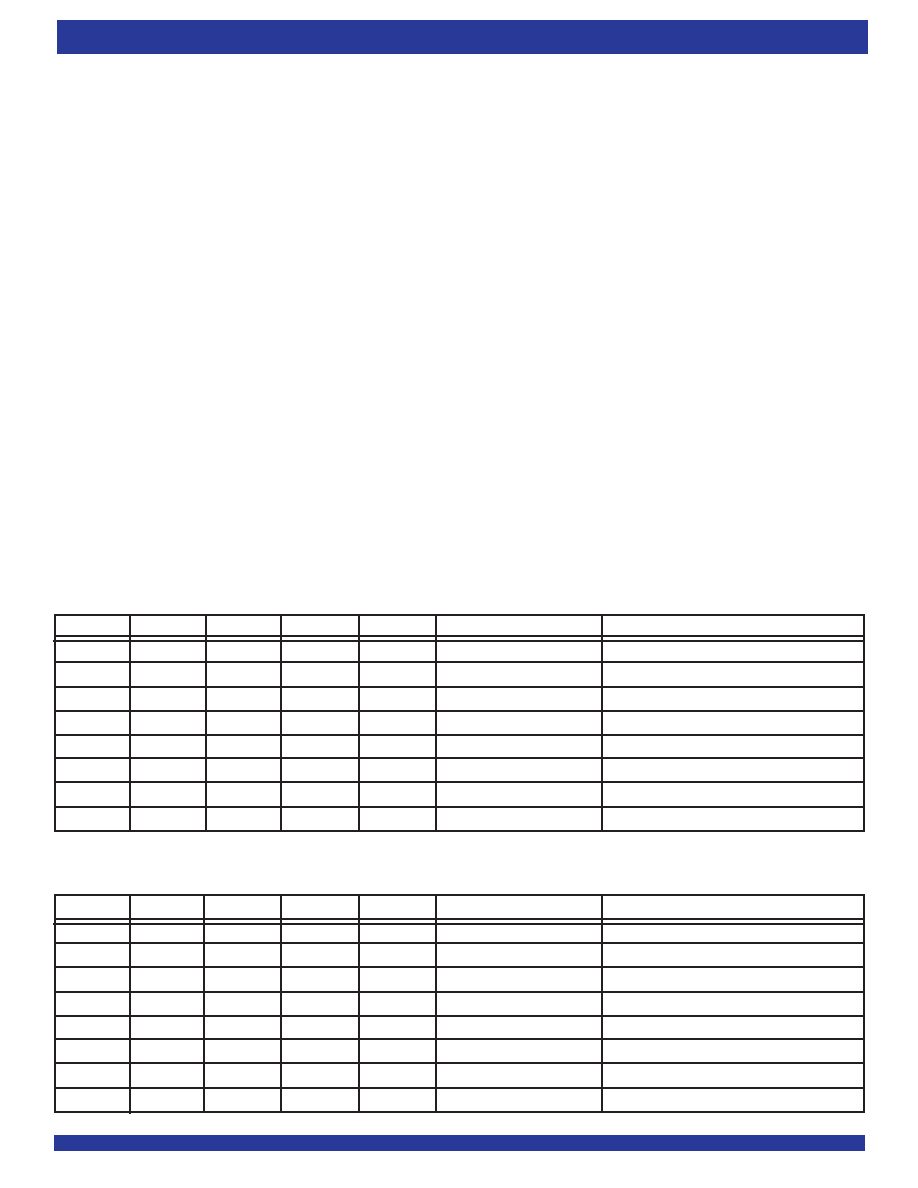

CSB

W/RB

ENB

MBB

CLKB

Data B (B0-A35) I/O

Port Functions

H

X

Input

None

L

X

Input

None

LL

H

L

↑

Input

None

LL

H

↑

Input

Mail2 Write

L

H

L

X

Output

None

LH

HL

↑

Output

FIFO read

L

H

L

H

X

Output

None

L

HHH

↑

Output

Mail1 Read (Set

MBF1 HIGH)

CSA

W/

RA

ENA

MBA

CLKA

Data A (A0-A35) I/O

Port Functions

H

X

Input

None

L

H

L

X

Input

None

LH

HL

↑

Input

FIFO Write

LH

H

↑

Input

Mail1 Write

L

X

Output

None

LL

H

L

↑

Output

None

L

H

X

Output

None

LL

H

↑

Output

Mail2 Read (Set

MBF2 HIGH)

TABLE 2 —

—

— PORT-A ENABLE FUNCTION TABLE

TABLE 3 —

—

— PORT-B ENABLE FUNCTION TABLE

相关PDF资料 |

PDF描述 |

|---|---|

| VE-26B-IU-F1 | CONVERTER MOD DC/DC 95V 200W |

| LTC1345ISW#TR | IC TXRX V.35 SGL SUPPLY 28SOIC |

| XRT6164CP-F | IC TXRX DGTL INTERFACE 16PDIP |

| IDT72V3632L10PF8 | IC BIFIFO 512X36X2 10NS 120-TQFP |

| VI-2WV-MY | CONVERTER MOD DC/DC 5.8V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT72V3631L15PQF | 功能描述:IC SYNCFIFO 512X36 15NS 132-PQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72V3631L20PF | 功能描述:IC SYNCFIFO 512X36 20NS 120-TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72V3631L20PF8 | 功能描述:IC SYNCFIFO 512X36 20NS 120-TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72V3631L20PQF | 功能描述:IC SYNCFIFO 512X36 20NS 132-PQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72V3632L10PF | 功能描述:IC BIFIFO 512X36X2 10NS 120-TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

发布紧急采购,3分钟左右您将得到回复。