- 您现在的位置:买卖IC网 > PDF目录377488 > IDT82V3002APV (INTEGRATED DEVICE TECHNOLOGY INC) WAN PLL WITH DUAL REFERENCE INPUTS PDF资料下载

参数资料

| 型号: | IDT82V3002APV |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 通信及网络 |

| 英文描述: | WAN PLL WITH DUAL REFERENCE INPUTS |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PDSO56 |

| 封装: | SSOP-56 |

| 文件页数: | 12/28页 |

| 文件大小: | 390K |

| 代理商: | IDT82V3002APV |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页当前第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

12

IDT82V3002A WAN PLL WITH DUAL REFERENCE INPUTS INDUSTRIAL TEMPERATURE RANGE

corresponds to the worst case of 18 frame (125 μs per frame) slips in 24

hours. This meets AT&T TR62411 and Telcordia GR-1244-CORE

Stratum 3 requirement of ±0.37 ppm (255 frame slips per 24 hours).

The HOLDOVER pin will be set to logic high whenever the

IDT82V3002A goes into Holdover Mode.

3.1.4

FREERUN MODE

Freerun Mode is typically used when a master clock source is

required, or a system is just powered up and the network

synchronization has not been achieved.

In Freerun Mode, the IDT82V3002A provides timing and

synchronization signals which are based on the master clock frequency

(OSCi) only and not synchronized to the input reference signal.

The accuracy of the output clock is equal to the accuracy of the

master clock (OSCi). So if a ±32 ppm output clock is required, the

master clock must also be ±32 ppm. Refer to

"OSC"

for more

information.

The FREERUN pin will go high whenever the IDT82V3002A works in

Freerun Mode.

3.2

FREQUENCY SELECT CIRCUIT

The input reference can be 8 kHz, 1.544 MHz or 2.048 MHz. As

shown in

Table - 3

, the F_sel1 and F_sel0 pins determine which of the

three frequencies is selected. Note that both the reference inputs Fref0

and Fref1 must have the same frequency applied to them. Every time

the frequency is changed, the device must be reset to make the change

effective.

3.3

REFERENCE INPUT SWITCH

The IDT82V3002A accepts two simultaneous reference input

signals, Fref0 and Fref1, and operates on their falling edges. The

reference is selected by the IN_sel pin, as shown in

Table - 4

. The

selected reference signal is sent to the TIE control block, Reference

Input Monitor and Invalid Input Signal Detection block to be further

processed.

When a transient voltage occurs at the IN_sel pin, the IDT82V3002A

will automatically switch to the Short Time Holdover Mode (S4) with the

TIE Control Block disabled. At the S4 stage, if no transient occurs on the

IN_sel pin, the reference signal will be changed from one to the other

and the device will switch back to Normal Mode (S1) automatically.

During the change from S4 to S1, the TIE Control Block can be manually

enabled or disabled. See

Figure - 4

for details.

3.4

REFERENCE INPUT MONITOR

Telcordia GR-1244-CORE standard recommends that a DPLL

should be able to reject the references that are off the nominal

frequency by more than ±12 ppm. The IDT82V3002A monitors the TIE

Control Block input frequency and outputs a signal on the MON_out pin

to indicate the result. Whenever the reference is off the nominal

frequency by more than ±12 ppm, the MON_out pin will go high. The

MON_out signal is updated every 2 seconds.

3.5

INVALID INPUT SIGNAL DETECTION

This circuit monitors the input reference signal into the

IDT82V3002A. The IDT82V3002A will automatically enter Holdover

Mode (Auto-Holdover) if the incoming reference signal is out of the

capture range (See

Table - 8

), including a complete loss of input

reference, or a large frequency shift in the input reference. When the

input reference returns to normal, the DPLL will return to Normal Mode.

In Holdover Mode, the output signal of the IDT82V3002A is based on

the output signal 30 ms to 60 ms prior to entering Holdover Mode. The

amount of phase drift in Holdover Mode is negligible because Holdover

Mode is very accurate (e.g., 0.025 ppm). Consequently, the phase delay

between the input and output after switching back to Normal Mode is

preserved.

3.6

TIE CONTROL BLOCK

If the current reference is badly damaged or lost, it is necessary to

use the other reference or the one generated by the storage techniques

instead. But when switching the reference, a step change in phase on

the input reference will occur. And a step change in phase at the input of

the DPLL would lead to unacceptable phase changes in the output

signals. The TIE control block, when enabled, prevents a step change in

phase on the input reference signals from causing a step change in

phase at the output of the DPLL block.

Figure - 5

shows the TIE Control

Block diagram.

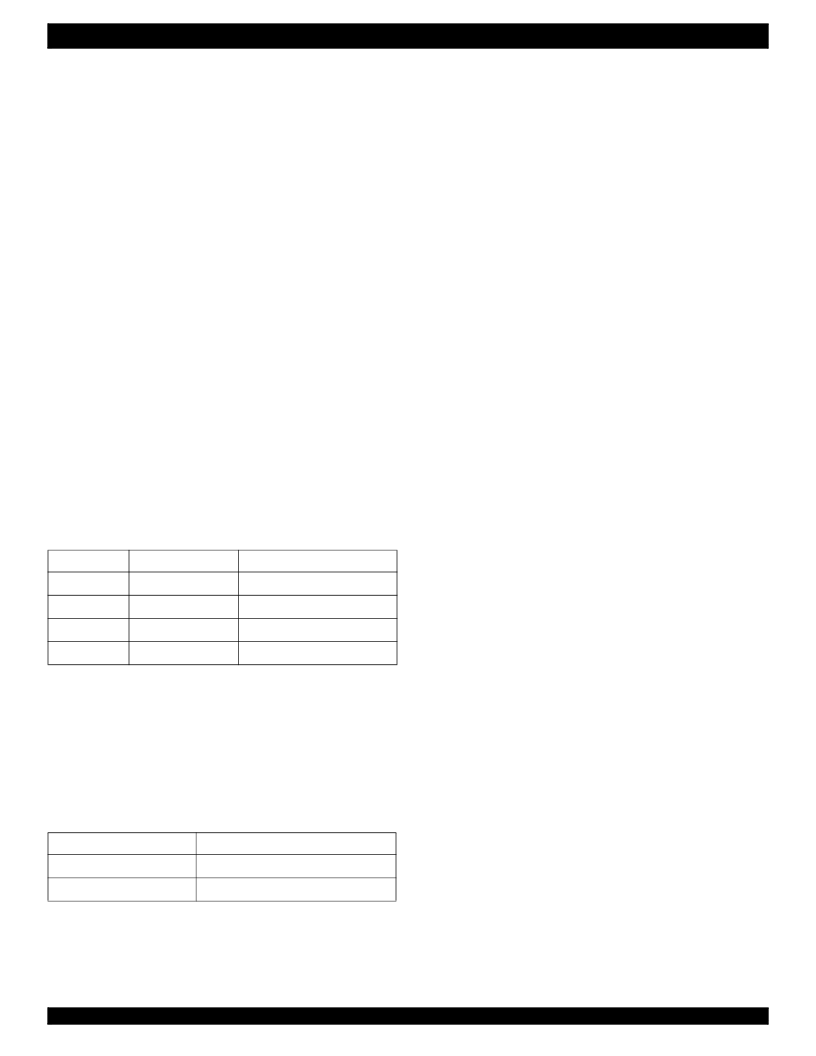

Table - 3 Input Reference Frequency Selection

F_sel1

F_sel0

Input Frequency

0

0

Reserved

0

1

8 kHz

1

0

1.544 MHz

1

1

2.048 MHz

Table - 4 Reference Input Switch Control

IN_sel

Input Reference

0

Fref0

1

Fref1

相关PDF资料 |

PDF描述 |

|---|---|

| IDT82V3010 | T1/E1/OC3 TELECOM CLOCK GENERATOR WITH DUAL REFERENCE INPUTS |

| IDT82V3010PV | T1/E1/OC3 TELECOM CLOCK GENERATOR WITH DUAL REFERENCE INPUTS |

| IDT82V3010PVG | T1/E1/OC3 TELECOM CLOCK GENERATOR WITH DUAL REFERENCE INPUTS |

| IDT82V3255 | WAN PLL |

| IDT82V3255DK | WAN PLL |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT82V3002APVG | 功能描述:IC PLL WAN T1/E1 DUAL REF 56SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| IDT82V3002APVG8 | 功能描述:IC PLL WAN T1/E1 DUAL REF 56SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| IDT82V3010 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:T1/E1/OC3 TELECOM CLOCK GENERATOR WITH DUAL REFERENCE INPUTS |

| IDT82V3010PV | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:T1/E1/OC3 TELECOM CLOCK GENERATOR WITH DUAL REFERENCE INPUTS |

| IDT82V3010PVG | 功能描述:IC PLL WAN 51/E1/OC3 DUAL 56SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

发布紧急采购,3分钟左右您将得到回复。