- 您现在的位置:买卖IC网 > PDF目录377488 > IDT82V3002APV (INTEGRATED DEVICE TECHNOLOGY INC) WAN PLL WITH DUAL REFERENCE INPUTS PDF资料下载

参数资料

| 型号: | IDT82V3002APV |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 通信及网络 |

| 英文描述: | WAN PLL WITH DUAL REFERENCE INPUTS |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PDSO56 |

| 封装: | SSOP-56 |

| 文件页数: | 23/28页 |

| 文件大小: | 390K |

| 代理商: | IDT82V3002APV |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页当前第23页第24页第25页第26页第27页第28页

23

IDT82V3002A WAN PLL WITH DUAL REFERENCE INPUTS INDUSTRIAL TEMPERATURE RANGE

*

Notes:

Voltages are with respect to ground (V

SS

) unless otherwise stated.

Supply voltage and operating temperature are as per Recommended Operating Conditions.

Timing parameters are as per AC Electrical Characteristics - Timing Parameter Measurement Voltage Levels

1.

2.

3.

4.

5.

6.

7.

8.

9.

10. Master clock input OSCi at 20 MHz ±32 ppm.

11.

Master clock input OSCi at 20 MHz ±100 ppm.

12. Selected reference input at

±

0 ppm.

13. Selected reference input at

±

32 ppm.

14. Selected reference input at

±

100 ppm.

15. For Freerun Mode of

±

0 ppm.

16. For Freerun Mode of

±

32 ppm.

17. For Freerun Mode of

±

100 ppm.

18. For capture range of

±

230 ppm.

19. For capture range of

±

198 ppm.

20. For capture range of

±

130 ppm.

21. 25 pF capacitive load.

22. OSCi Master Clock jitter is less than 2 nspp, or 0.04 UIpp where 1 UIpp = 1/20 MHz.

23. Jitter on reference input is obtained at slightly higher input jitter amplitudes.

24. Applied jitter is sinusoidal.

25. Minimum applied input jitter magnitude to regain synchronization.

26. Loss of synchronization is obtained at slightly higher input jitter amplitudes.

27. Within 10 ms of the state, reference or input change.

28. 1 UIpp = 125 μs for 8 kHz signals.

29. 1 UIpp = 648 ns for 1.544 MHz signals.

30. 1 UIpp = 488 ns for 2.048 MHz signals.

31. 1 UIpp = 323 ns for 3.088 MHz signals.

32. 1 UIpp = 244 ns for 4.096 MHz signals.

33. 1 UIpp = 122 ns for 8.192 MHz signals.

34. 1 UIpp = 61 ns for 16.484 MHz signals.

35. 1 UIpp = 30 ns for 32.968 MHz signals.

36. No filter.

37. 40 Hz to 100 kHz bandpass filter.

38. With respect to reference input signal frequency.

39. After chip reset or TIE reset.

40. Master clock duty 40% to 60%.

41. Prior to Holdover Mode, device as in Normal Mode and phase locked.

42. With input frequency offset of 100 ppm.

Fref0 reference input selected.

Fref1 reference input selected.

Normal Mode selected.

Holdover Mode selected.

Freerun Mode selected.

8 kHz Frequency Mode selected.

1.544 MHz Frequency Mode selected.

2.048 MHz Frequency Mode selected.

Master clock input OSCi at 20 MHz ±0 ppm.

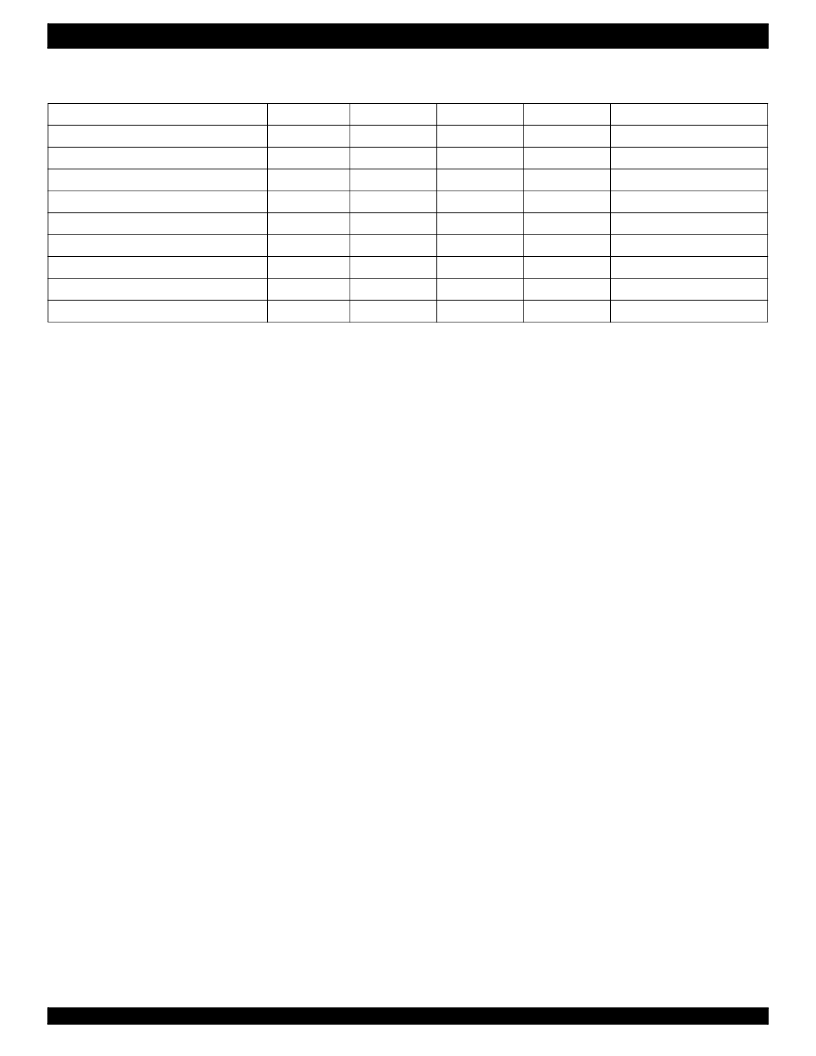

Table - 17 2.048 MHz Input Jitter Tolerance

Description

Min

Typ

Max

Units

Test Conditions / Notes*

Jitter tolerance for 1 Hz input

150

UIpp

1-3, 8, 9-14, 21-22, 24-26, 30

Jitter tolerance for 5 Hz input

140

UIpp

1-3, 8, 9-14, 21-22, 24-26, 30

Jitter tolerance for 20 Hz input

130

UIpp

1-3, 8, 9-14, 21-22, 24-26, 30

Jitter tolerance for 300 Hz input

40

UIpp

1-3, 8, 9-14, 21-22, 24-26, 30

Jitter tolerance for 400 Hz input

33

UIpp

1-3, 8, 9-14, 21-22, 24-26, 30

Jitter tolerance for 700 Hz input

18

UIpp

1-3, 8, 9-14, 21-22, 24-26, 30

Jitter tolerance for 2400 Hz input

5.5

UIpp

1-3, 8, 9-14, 21-22, 24-26, 30

Jitter tolerance for 10 kHz input

1.3

UIpp

1-3, 8, 9-14, 21-22, 24-26, 30

Jitter tolerance for 100 kHz input

0.4

UIpp

1-3, 8, 9-14, 21-22, 24-26, 30

相关PDF资料 |

PDF描述 |

|---|---|

| IDT82V3010 | T1/E1/OC3 TELECOM CLOCK GENERATOR WITH DUAL REFERENCE INPUTS |

| IDT82V3010PV | T1/E1/OC3 TELECOM CLOCK GENERATOR WITH DUAL REFERENCE INPUTS |

| IDT82V3010PVG | T1/E1/OC3 TELECOM CLOCK GENERATOR WITH DUAL REFERENCE INPUTS |

| IDT82V3255 | WAN PLL |

| IDT82V3255DK | WAN PLL |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT82V3002APVG | 功能描述:IC PLL WAN T1/E1 DUAL REF 56SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| IDT82V3002APVG8 | 功能描述:IC PLL WAN T1/E1 DUAL REF 56SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| IDT82V3010 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:T1/E1/OC3 TELECOM CLOCK GENERATOR WITH DUAL REFERENCE INPUTS |

| IDT82V3010PV | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:T1/E1/OC3 TELECOM CLOCK GENERATOR WITH DUAL REFERENCE INPUTS |

| IDT82V3010PVG | 功能描述:IC PLL WAN 51/E1/OC3 DUAL 56SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

发布紧急采购,3分钟左右您将得到回复。