- 您现在的位置:买卖IC网 > PDF目录19507 > ADSP-2185NKSTZ-320 (Analog Devices Inc)IC DSP CONTROLLER 16BIT 100LQFP PDF资料下载

参数资料

| 型号: | ADSP-2185NKSTZ-320 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 23/48页 |

| 文件大小: | 0K |

| 描述: | IC DSP CONTROLLER 16BIT 100LQFP |

| 标准包装: | 1 |

| 系列: | ADSP-21xx |

| 类型: | 定点 |

| 接口: | 主机接口,串行端口 |

| 时钟速率: | 80MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 80kB |

| 电压 - 输入/输出: | 1.8V,2.5V,3.3V |

| 电压 - 核心: | 1.80V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 100-LQFP |

| 供应商设备封装: | 100-LQFP(14x14) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页当前第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

ADSP-218xN

Rev. A

|

Page 3 of 48

|

August 2006

GENERAL DESCRIPTION

The ADSP-218xN series consists of six single chip microcom-

puters optimized for digital signal processing applications. The

high-level block diagram for the ADSP-218xN series members

appears on the previous page. All series members are pin-com-

patible and are differentiated solely by the amount of on-chip

SRAM. This feature, combined with ADSP-21xx code compati-

bility, provides a great deal of flexibility in the design decision.

Specific family members are shown in Table 1.

ADSP-218xN series members combine the ADSP-2100 family

base architecture (three computational units, data address gen-

erators, and a program sequencer) with two serial ports, a 16-bit

internal DMA port, a byte DMA port, a programmable timer,

Flag I/O, extensive interrupt capabilities, and on-chip program

and data memory.

ADSP-218xN series members integrate up to 256K bytes of on-

chip memory configured as up to 48K words (24-bit) of pro-

gram RAM, and up to 56K words (16-bit) of data RAM. Power-

down circuitry is also provided to meet the low power needs of

battery-operated portable equipment. The ADSP-218xN is

available in a 100-lead LQFP package and 144-ball BGA.

Fabricated in a high-speed, low-power, 0.18 μm CMOS process,

ADSP-218xN series members operate with a 12.5 ns instruction

cycle time. Every instruction can execute in a single pro-

cessor cycle.

The ADSP-218xN’s flexible architecture and comprehensive

instruction set allow the processor to perform multiple opera-

tions in parallel. In one processor cycle, ADSP-218xN series

members can:

Generate the next program address

Fetch the next instruction

Perform one or two data moves

Update one or two data address pointers

Perform a computational operation

This takes place while the processor continues to:

Receive and transmit data through the two serial ports

Receive and/or transmit data through the internal

DMA port

Receive and/or transmit data through the byte DMA port

Decrement timer

ARCHITECTURE OVERVIEW

The ADSP-218xN series instruction set provides flexible data

moves and multifunction (one or two data moves with a com-

putation) instructions. Every instruction can be executed in a

single processor cycle. The ADSP-218xN assembly language

uses an algebraic syntax for ease of coding and readability. A

comprehensive set of development tools supports program

development.

The functional block diagram is an overall block diagram of the

ADSP-218xN series. The processor contains three independent

computational units: the ALU, the multiplier/accumulator

(MAC), and the shifter. The computational units process 16-bit

data directly and have provisions to support multiprecision

computations. The ALU performs a standard set of arithmetic

and logic operations; division primitives are also supported. The

MAC performs single-cycle multiply, multiply/add, and multi-

ply/subtract operations with 40 bits of accumulation. The shifter

performs logical and arithmetic shifts, normalization, denor-

malization, and derive exponent operations.

The shifter can be used to efficiently implement numeric format

control, including multiword and block floating-point

representations.

The internal result (R) bus connects the computational units so

that the output of any unit may be the input of any unit on the

next cycle.

A powerful program sequencer and two dedicated data address

generators ensure efficient delivery of operands to these compu-

tational units. The sequencer supports conditional jumps,

subroutine calls, and returns in a single cycle. With internal

loop counters and loop stacks, ADSP-218xN series members

execute looped code with zero overhead; no explicit jump

instructions are required to maintain loops.

Two data address generators (DAGs) provide addresses for

simultaneous dual operand fetches (from data memory and pro-

gram memory). Each DAG maintains and updates four address

pointers. Whenever the pointer is used to access data (indirect

addressing), it is post-modified by the value of one of four possi-

ble modify registers. A length value may be associated with each

pointer to implement automatic modulo addressing for

circular buffers.

Five internal buses provide efficient data transfer:

Program Memory Address (PMA) Bus

Program Memory Data (PMD) Bus

Data Memory Address (DMA) Bus

Data Memory Data (DMD) Bus

Result (R) Bus

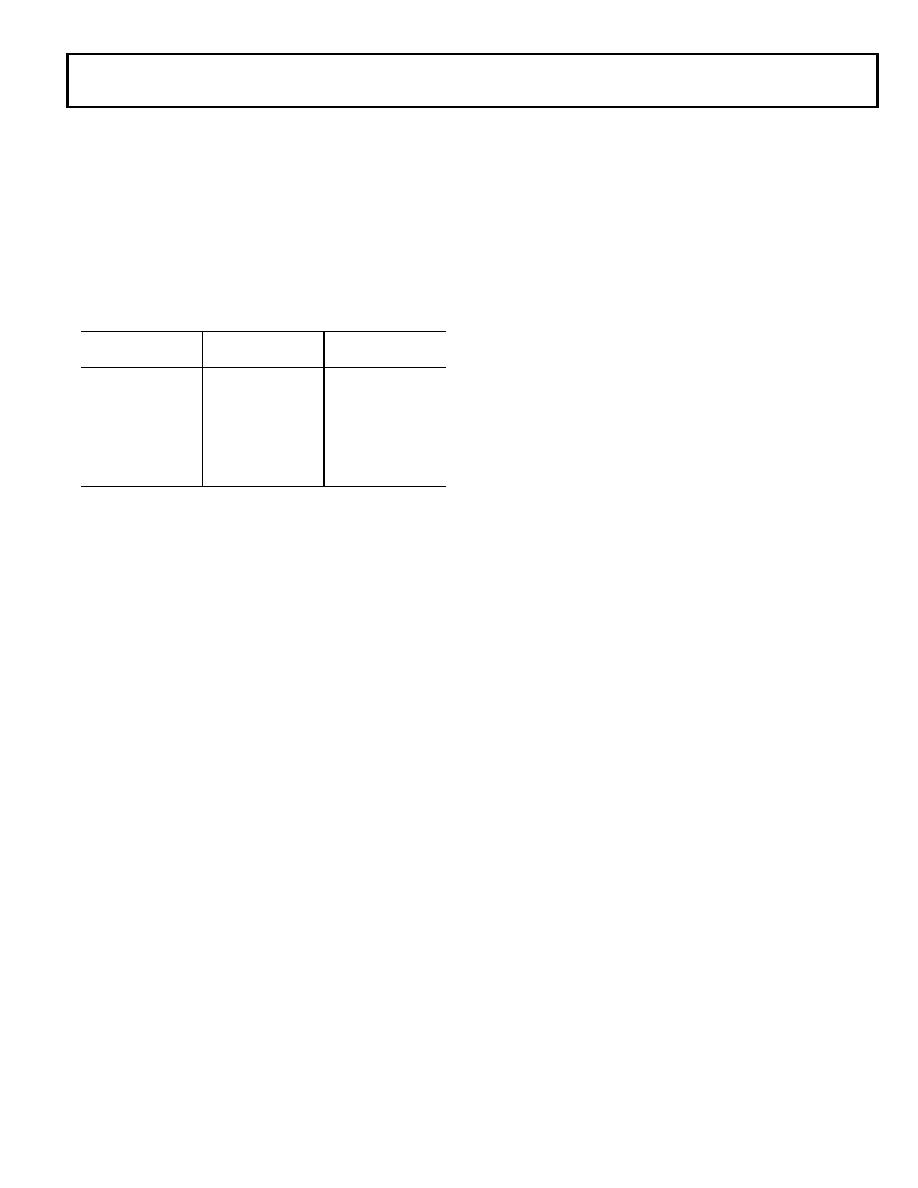

Table 1. ADSP-218xN DSP Microcomputer Family

Device

Program Memory

(K words)

Data Memory

(K words)

ADSP-2184N

4

ADSP-2185N

16

ADSP-2186N

8

ADSP-2187N

32

ADSP-2188N

48

56

ADSP-2189N

32

48

相关PDF资料 |

PDF描述 |

|---|---|

| AMM15DTAN-S189 | CONN EDGECARD 30POS R/A .156 SLD |

| GSM36DSAN | CONN EDGECARD 72POS R/A .156 SLD |

| GMM36DSAN | CONN EDGECARD 72POS R/A .156 SLD |

| GEM25DSEH-S243 | CONN EDGECARD 50POS .156 EYELET |

| NTV0515MC | CONV DC/DC 1W 5VIN 15VOUT DL 3KV |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL12028IVZ-T | 功能描述:实时时钟 REAL TIME CLKRTC W/ EPROM IN 14LD T RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube |

| ISL12029 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Real Time Clock/Calendar with I2C Bus? and EEPROM |

| ISL12029_10 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Real Time Clock/Calendar with I2C Busa?¢ and EEPROM |

| ISL12029_1012 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Real Time Clock/Calendar with I2C Bus? and EEPROM |

| ISL12029A | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Real Time Clock/Calendar with I2C Bus? and EEPROM |

发布紧急采购,3分钟左右您将得到回复。