- 您现在的位置:买卖IC网 > PDF目录177663 > LC4256V-3FN256BC (LATTICE SEMICONDUCTOR CORP) PDF资料下载

参数资料

| 型号: | LC4256V-3FN256BC |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | PLD |

| 中文描述: | EE PLD, 3 ns, PBGA256 |

| 封装: | LEAD FREE, FPBGA-256 |

| 文件页数: | 98/99页 |

| 文件大小: | 441K |

| 代理商: | LC4256V-3FN256BC |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页当前第98页第99页

Lattice Semiconductor

ispMACH 4000V/B/C/Z Family Data Sheet

98

For Further Information

In addition to this data sheet, the following technical notes may be helpful when designing with the ispMACH

4000V/B/C/Z family:

ispMACH 4000 Timing Model Design and Usage Guidelines (TN1004)

ispMACH 4000V/B/C/Z Power Consumption (TN1005)

Revision History

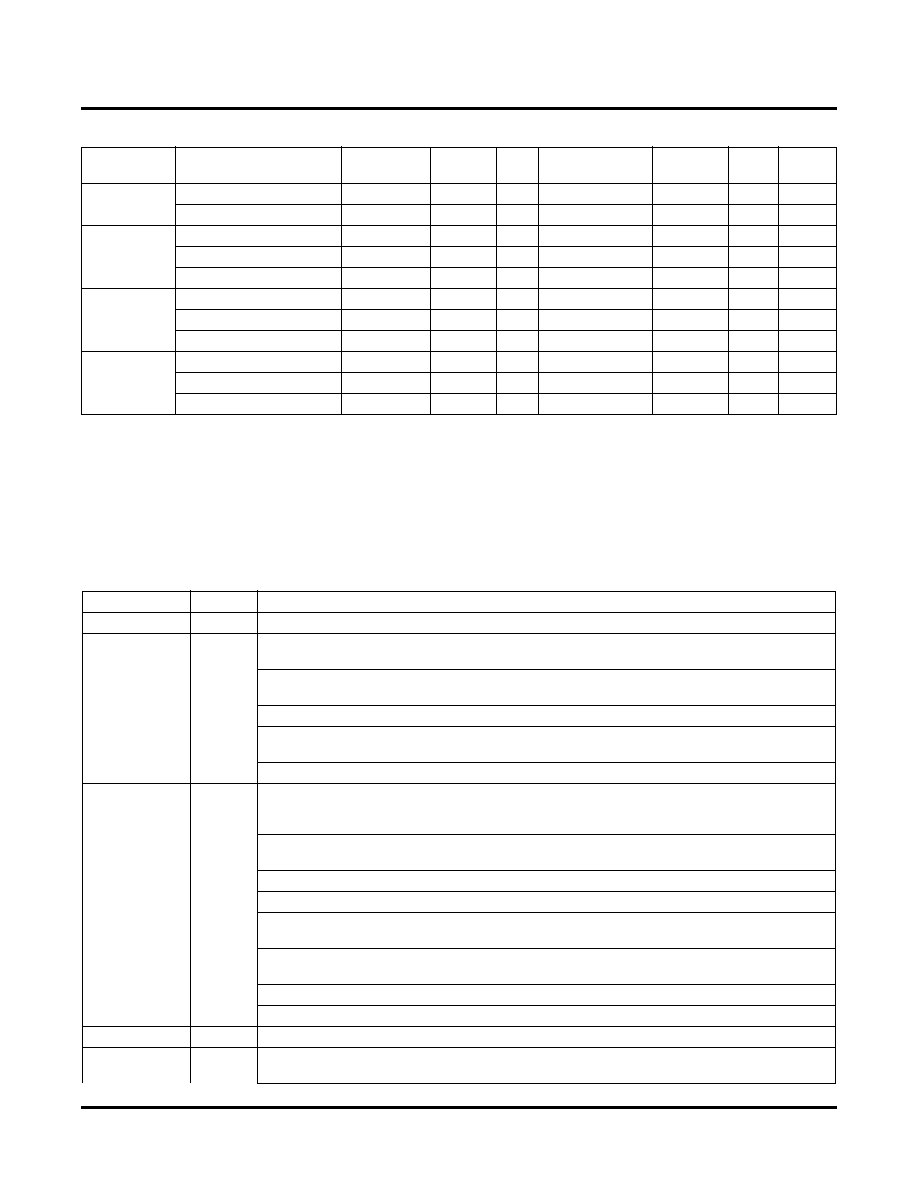

ispMACH 4000V (3.3V) Lead-Free Extended Temperature Devices

Device

Part Number

Macrocells

Voltage

tPD

Package

Pin/Ball

Count

I/O

Grade

LC4032V

LC4032V-75TN48E

32

3.3

7.5

Lead-free TQFP

48

32

E

LC4032V-75TN44E

32

3.3

7.5

Lead-free TQFP

44

30

E

LC4064V

LC4064V-75TN100E

64

3.3

7.5

Lead-free TQFP

100

64

E

LC4064V-75TN48E

64

3.3

7.5

Lead-free TQFP

48

32

E

LC4064V-75TN44E

64

3.3

7.5

Lead-free TQFP

44

30

E

LC4128V

LC4128V-75TN144E

128

3.3

7.5

Lead-free TQFP

144

96

E

LC4128V-75TN128E

128

3.3

7.5

Lead-free TQFP

128

92

E

LC4128V-75TN100E

128

3.3

7.5

Lead-free TQFP

100

64

E

LC4256V

LC4256V-75TN176E

256

3.3

7.5

Lead-free TQFP

176

128

E

LC4256V-75TN144E

256

3.3

7.5

Lead-free TQFP

144

96

E

LC4256V-75TN100E

256

3.3

7.5

Lead-free TQFP

100

64

E

Date

Version

Change Summary

—

Previous Lattice releases.

July 2003

17z

Changed device status for LC4064ZC and LC4128ZC to production release and updated/added

AC and DC parameters as well as ordering part numbers for LC4064ZC and LC4128ZC devices.

Improved leakage current specications for ispMACH 4000Z. For ispMACH 4000V/B/C IIL, IIH

condition now includes 0V and 3.6V end points (0 ≤ VIN ≤ 3.6V).

Added 132-ball chip scale BGA power supply and NC connections.

Added 132-ball chip scale BGA logic signal connections for LC4064ZC, LC4128ZC and

LC4256ZC devices.

Added lead-free package designators.

October 2003

18z

Hot socketing characteristics footnote 1. has been enhanced; Insensitive to sequence of VCC or

VCCO. However, assumes monotonic rise/fall rates for Vcc and Vcco, provided (VIN - VCCO) ≤

3.6V.

Improved LC4064ZC tS to 2.5ns, tST to 2.7ns and fMAX (Ext.) to 175MHz, LC4128ZC tCO to

3.5ns and fMAX (Ext.) to 161MHz (version v.2.1).

Improved associated internal timing numbers and timing adders (version v.2.1).

Added ispMACH 4000V/B/C/Z ORP Reference Tables.

Enhanced ORP information in device pinout tables consistent with the ORP Combinations for I/O

Blocks tables (table 6, 7, 8 and 9 in page 9-11).

Corrected GLB/MC/Pad information in the 256-fpBGA pinouts for the LC4256V/B/C 160-I/O ver-

sion.

Added the ispMACH 4000 Family Speed Grade Offering table.

Added the ispMACH 4128ZC Industrial and Automotive Device OPNs

December 2003

19z

Added the ispMACH 4032ZC and 4064ZC Industrial and Automotive Device OPNs

January 2004

20z

ispMACH 4000Z data sheet status changed from preliminary to nal. Documents production

release of the ispMACH 4256Z device.

相关PDF资料 |

PDF描述 |

|---|---|

| LC4512B-5FN256I | |

| LC4384V-5FN256C | |

| LC4512V-35FN256C | |

| LC4256B-75FN256BC | |

| LC4256B-75FN256BI | |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LC4256V-3FN256BC1 | 制造商:LATTICE 制造商全称:Lattice Semiconductor 功能描述:3.3V/2.5V/1.8V In-System Programmable SuperFAST High Density PLDs |

| LC4256V-3FT256AC | 功能描述:CPLD - 复杂可编程逻辑器件 ispJTAG 3.3V 3ns 256MC 128 I/O RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| LC4256V-3FT256BC | 功能描述:CPLD - 复杂可编程逻辑器件 ispJTAG 3.3V 3ns 256MC 160 I/O RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| LC4256V-3FTN256AC | 功能描述:CPLD - 复杂可编程逻辑器件 ispJTAG 3.3V 3ns 256MC 128 I/O RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| LC4256V-3FTN256BC | 功能描述:CPLD - 复杂可编程逻辑器件 ispJTAG 3.3V 3ns 256MC 160 I/O RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

发布紧急采购,3分钟左右您将得到回复。