- 您现在的位置:买卖IC网 > PDF目录69021 > MB91108PFV 32-BIT, 50 MHz, RISC MICROCONTROLLER, PQFP120 PDF资料下载

参数资料

| 型号: | MB91108PFV |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 50 MHz, RISC MICROCONTROLLER, PQFP120 |

| 封装: | PLASTIC, LQFP-120 |

| 文件页数: | 56/96页 |

| 文件大小: | 1342K |

| 代理商: | MB91108PFV |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页当前第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页

MB91107/108

6

(Continued)

Pin no.

Pin name

Circuit

type

Function

80

BGRNT/P81

F

External bus release acknowledge output.

Outputs “L” level when external bus is released.

Can be configured as a port when this pin is not used.

81

BRQ/P82

P

External bus release request input.

Inputs “1” when release of external bus is required.

Can be configured as a port when this pin is not used.

82

RD

M

Read strobe output pin for external bus.

83

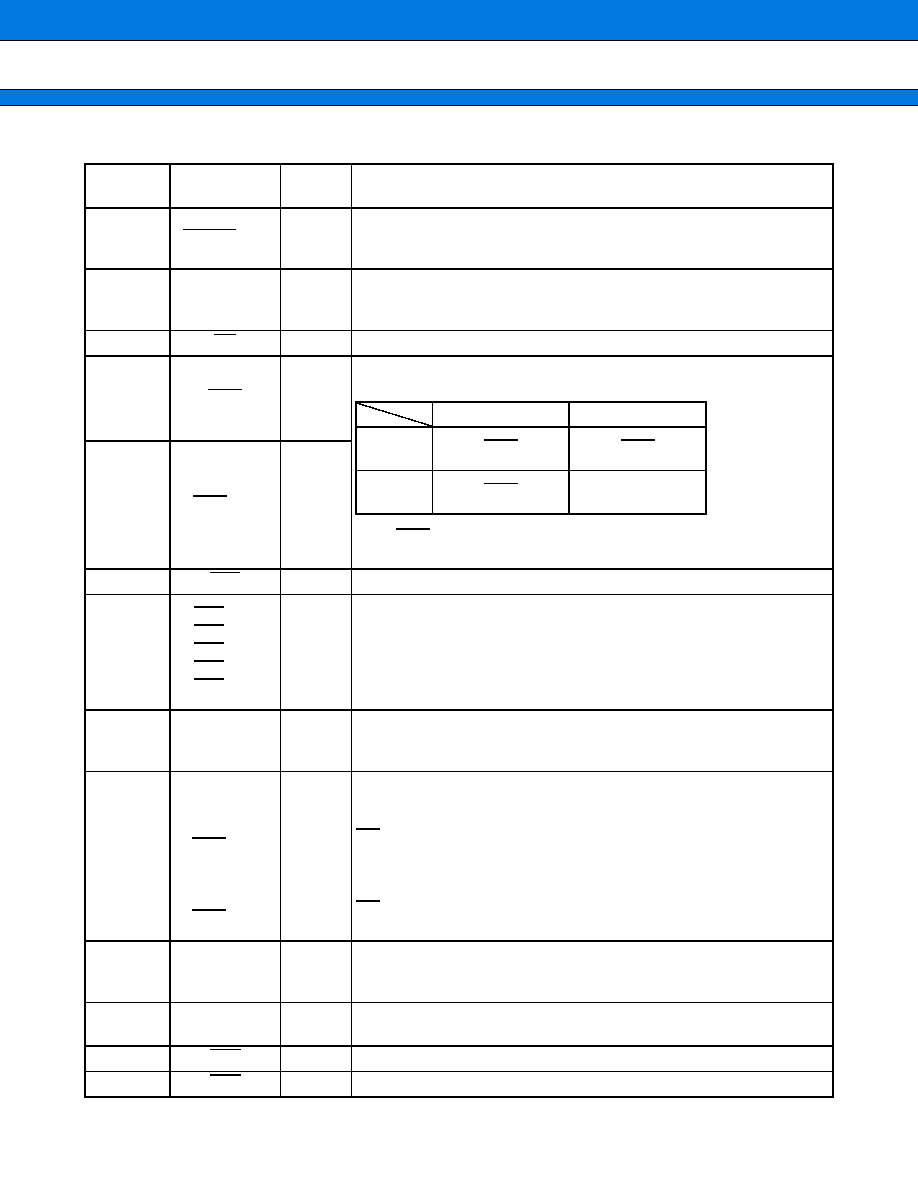

WR0

M

Write strobe output pin for external bus. Relation between control signals

and effective byte locations is as follows:

Note: WR1 is Hi-Z during resetting. Attach an external pull-up resister

when using at 16-bit bus width.

84

WR1/P85

F

65

CS0

M

Chip select 0 output (“L” active).

66

67

68

69

70

CS1/PA1

CS2/PA2

CS3/PA3

CS4/PA4

CS5/PA5

F

Chip select 1 output (“L” active).

Chip select 2 output (“L” active).

Chip select 3 output (“L” active).

Chip select 4 output (“L” active).

Chip select 5 output (“L” active).

Can be configured as ports when PA1 to PA5 are not used.

71

CLK/PA6

F

System clock output.

Outputs clock signal of external bus operating frequency.

Can be configured as a port when PA6 is not used.

56

57

58

59

60

61

62

63

RAS0/PB0

CS0L/PB1

CS0H/PB2

DW0/PB3

RAS1/PB4

CS1L/PB5

CS1H/PB6

DW1/PB7

F

RAS output for DRAM bank 0.

CASL output for DRAM bank 0.

CASH output for DRAM bank 0.

WE output for DRAM bank 0 (“L” active).

RAS output for DRAM bank 1.

CASL output for DRAM bank 1.

CASH output for DRAM bank 1.

WE output for DRAM bank 1 (“L” active)

Can be configured as a port when PB0 to PB7 are not used.

76

77

78

MD0

MD1

MD2

G

Mode pins 0 to 2.

MCU basic operation mode is set by these pins.

Directly connect these pins with VCC or VSS for use.

53

54

X1

X0

A

Clock (oscillator) output.

Clock (oscillator) input.

74

RST

B

External reset input.

73

HST

H

Hardware standby input (“L” active).

16-bit bus width

8-bit bus width

D31 to

D24

WR0

D23 to

D16

WR1

(I/O port enabled)

Refer to the

DRAM interface

for details.

相关PDF资料 |

PDF描述 |

|---|---|

| MB91107PFV | 32-BIT, 50 MHz, RISC MICROCONTROLLER, PQFP120 |

| MB91110PMT2 | 32-BIT, 50 MHz, RISC MICROCONTROLLER, PQFP144 |

| MB91110PMT2 | 32-BIT, 50 MHz, RISC MICROCONTROLLER, PQFP144 |

| MB91121PFV | 32-BIT, 50 MHz, RISC MICROCONTROLLER, PQFP120 |

| MB91154PFV-G-XXX | 32-BIT, MROM, 33 MHz, RISC MICROCONTROLLER, PQFP144 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MB91110 | 制造商:FUJITSU 制造商全称:Fujitsu Component Limited. 功能描述:32-Bit RISC Microcontroller |

| MB911110PMT2 | 制造商:FUJITSU 制造商全称:Fujitsu Component Limited. 功能描述:32-Bit RISC Microcontroller |

| MB91121 | 制造商:FUJITSU 制造商全称:Fujitsu Component Limited. 功能描述:32-bit RISC Microcontroller |

| MB91121PFV | 制造商:FUJITSU 制造商全称:Fujitsu Component Limited. 功能描述:32-bit RISC Microcontroller CMOS |

| MB91133 | 制造商:FUJITSU 制造商全称:Fujitsu Component Limited. 功能描述:32-Bit RISC Microcontroller |

发布紧急采购,3分钟左右您将得到回复。