参数资料

| 型号: | X40420S14I-BT1 |

| 厂商: | Intersil |

| 文件页数: | 11/25页 |

| 文件大小: | 0K |

| 描述: | IC VOLT MON DUAL SUP/SW 14-SOIC |

| 标准包装: | 2,500 |

| 类型: | 多压监控器 |

| 监视电压数目: | 2 |

| 输出: | 开路漏极,开路漏极 |

| 复位: | 高有效/低有效 |

| 复位超时: | 可调节/可选择 |

| 电压 - 阀值: | 2.6V,4.6V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 14-SOIC(0.154",3.90mm 宽) |

| 供应商设备封装: | 14-SOICN |

| 包装: | 带卷 (TR) |

�� �

�

�

�X40420,� X40421�

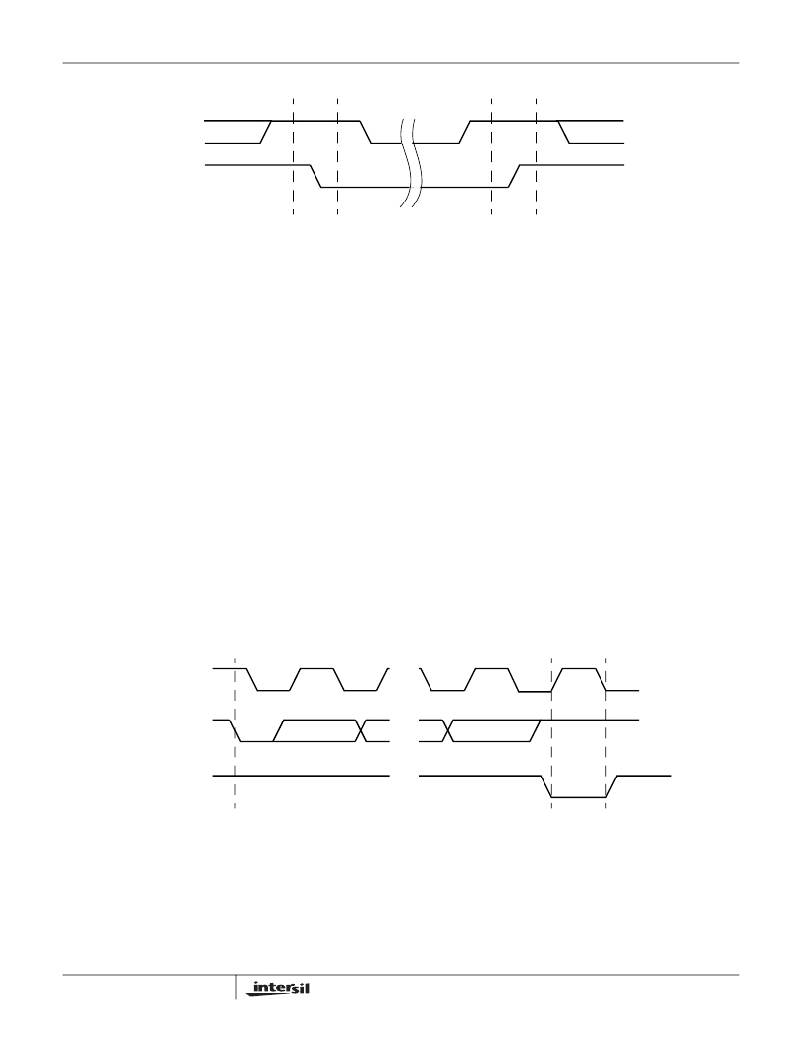

�Figure� 8.� Valid� Start� and� Stop� Conditions�

�SCL�

�SDA�

�Start�

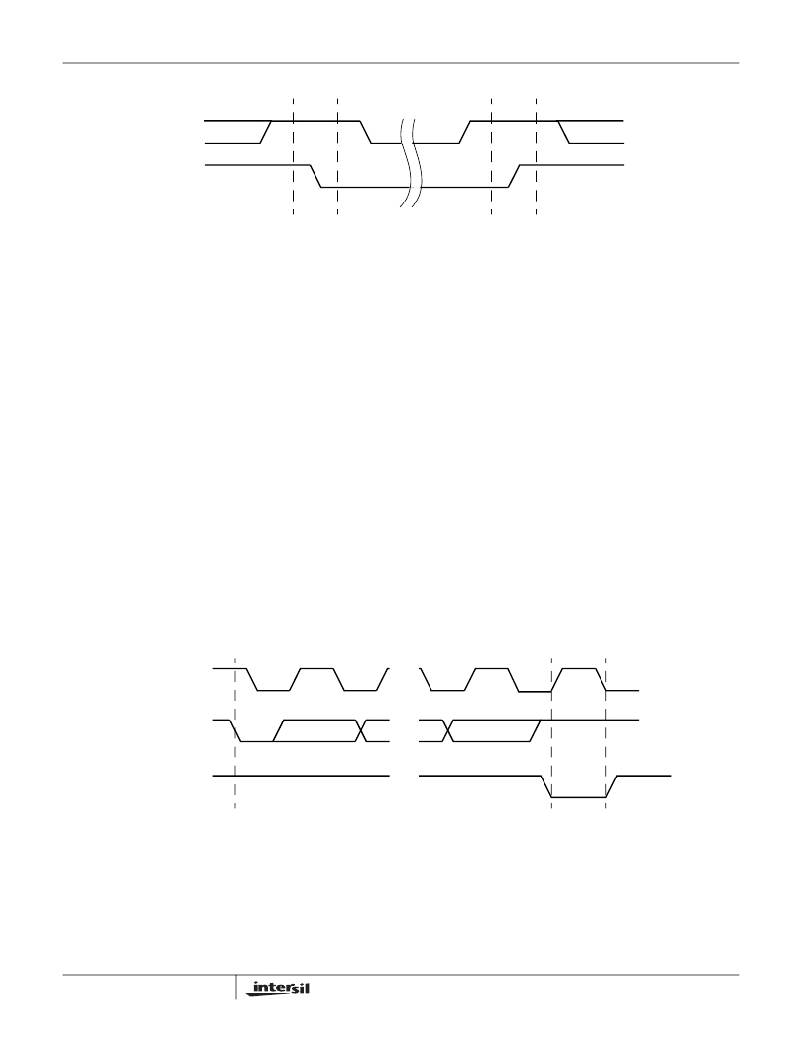

�Serial� Acknowledge�

�Acknowledge� is� a� software� convention� used� to� indi-�

�cate� successful� data� transfer.� The� transmitting� device,�

�either� master� or� slave,� will� release� the� bus� after� trans-�

�mitting� eight� bits.� During� the� ninth� clock� cycle,� the�

�receiver� will� pull� the� SDA� line� LOW� to� acknowledge�

�that� it� received� the� eight� bits� of� data.� See� Figure� 9.�

�The� device� will� respond� with� an� acknowledge� after�

�recognition� of� a� start� condition� and� if� the� correct�

�Device� Identifier� and� Select� bits� are� contained� in� the�

�Slave� Address� Byte.� If� a� write� operation� is� selected,�

�the� device� will� respond� with� an� acknowledge� after� the�

�receipt� of� each� subsequent� eight� bit� word.� The� device�

�will� acknowledge� all� incoming� data� and� address� bytes,�

�except� for� the� Slave� Address� Byte� when� the� Device�

�Identifier� and/or� Select� bits� are� incorrect.�

�In� the� read� mode,� the� device� will� transmit� eight� bits� of�

�data,� release� the� SDA� line,� then� monitor� the� line� for� an�

�acknowledge.� If� an� acknowledge� is� detected� and� no�

�stop� condition� is� generated� by� the� master,� the� device�

�will� continue� to� transmit� data.� The� device� will� terminate�

�further� data� transmissions� if� an� acknowledge� is� not�

�Figure� 9.� Acknowledge� Response� From� Receiver�

�Stop�

�detected.� The� master� must� then� issue� a� stop� condition�

�to� return� the� device� to� Standby� mode� and� place� the�

�device� into� a� known� state.�

�Serial� Write� Operations�

�Byte� Write�

�For� a� write� operation,� the� device� requires� the� Slave�

�Address� Byte� and� a� Word� Address� Byte.� This� gives�

�the� master� access� to� any� one� of� the� words� in� the�

�array.� After� receipt� of� the� Word� Address� Byte,� the�

�device� responds� with� an� acknowledge,� and� awaits� the�

�next� eight� bits� of� data.� After� receiving� the� 8� bits� of� the�

�Data� Byte,� the� device� again� responds� with� an�

�acknowledge.� The� master� then� terminates� the� transfer�

�by� generating� a� stop� condition,� at� which� time� the�

�device� begins� the� internal� write� cycle� to� the� nonvolatile�

�memory.� During� this� internal� write� cycle,� the� device�

�inputs� are� disabled,� so� the� device� will� not� respond� to� any�

�requests� from� the� master.� The� SDA� output� is� at� high�

�impedance.� See� Figure� 12.�

�A� write� to� a� protected� block� of� memory� will� suppress�

�the� acknowledge� bit.�

�SCL� from�

�Master�

�1�

�8�

�9�

�Data� Output�

�from�

�Data� Output�

�from� Receiver�

�Start�

�11�

�Acknowledge�

�May� 25,� 2006�

�相关PDF资料 |

PDF描述 |

|---|---|

| MAX1585ETJ+T | IC DGTL CAM PWR-SUP 5CH 32TQFN |

| X40420S14I-B | IC VOLT MON DUAL SUP/SW 14-SOIC |

| MAX1584ETJ+T | IC DGTL CAM PWR-SUP 5CH 32TQFN |

| X40420S14I-AT1 | IC VOLT MON DUAL SUP/SW 14-SOIC |

| X40420S14I-A | IC VOLT MON DUAL SUP/SW 14-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MC68331CPV16B1 | 制造商:Rochester Electronics LLC 功能描述:32BIT MCU,GPT,SIM,QSM - Bulk |

| MC68331CPV20 | 制造商:Rochester Electronics LLC 功能描述:32BIT MCU,GPT,SIM,QSM - Bulk |

| MC68331CPV20B1 | 制造商:Rochester Electronics LLC 功能描述:32BIT MCU,GPT,SIM,QSM - Bulk |

| MC68331CPV25 | 制造商:Rochester Electronics LLC 功能描述:32BIT MCU,GPT,SIM,QSM - Bulk |

| MC68331LPV20 | 制造商:Motorola Inc 功能描述: |

发布紧急采购,3分钟左右您将得到回复。