- 您现在的位置:买卖IC网 > PDF目录132989 > MCIMX31LCVMN4C (FREESCALE SEMICONDUCTOR INC) 32-BIT, 400 MHz, MICROPROCESSOR, PBGA473 PDF资料下载

参数资料

| 型号: | MCIMX31LCVMN4C |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 400 MHz, MICROPROCESSOR, PBGA473 |

| 封装: | 19 X 19 MM, 0.80 MM PITCH, ROHS COMPLIANT, PLASTIC, BGA-473 |

| 文件页数: | 64/108页 |

| 文件大小: | 2878K |

| 代理商: | MCIMX31LCVMN4C |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页当前第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页

Electrical Characteristics

MCIMX31C/MCIMX31LC Technical Data, Rev. 4.3

Freescale Semiconductor

59

4.3.15.4

Synchronous Interface to Dual-Port Smart Displays

Functionality and electrical characteristics of the synchronous interface to dual-port smart displays are

identical to parameters of the synchronous interface. See Section 4.3.15.2.2, “Interface to Active Matrix

4.3.15.4.1

Interface to a TV Encoder, Functional Description

The interface has an 8-bit data bus, transferring a single 8-bit value (Y/U/V) in each cycle. The bits

D7–D0 of the value are mapped to bits LD17–LD10 of the data bus, respectively. Figure 50 depicts the

interface timing,

The frequency of the clock DISPB_D3_CLK is 27 MHz (within 10%).

The DISPB_D3_HSYNC, DISPB_D3_VSYNC and DISPB_D3_DRDY signals are active low.

The transition to the next row is marked by the negative edge of the DISPB_D3_HSYNC signal.

It remains low for a single clock cycle.

The transition to the next field/frame is marked by the negative edge of the DISPB_D3_VSYNC

signal. It remains low for at least one clock cycle.

— At a transition to an odd field (of the next frame), the negative edges of DISPB_D3_VSYNC

and DISPB_D3_HSYNC coincide.

— At a transition to an even field (of the same frame), they do not coincide.

The active intervals—during which data is transferred—are marked by the DISPB_D3_HSYNC

signal being high.

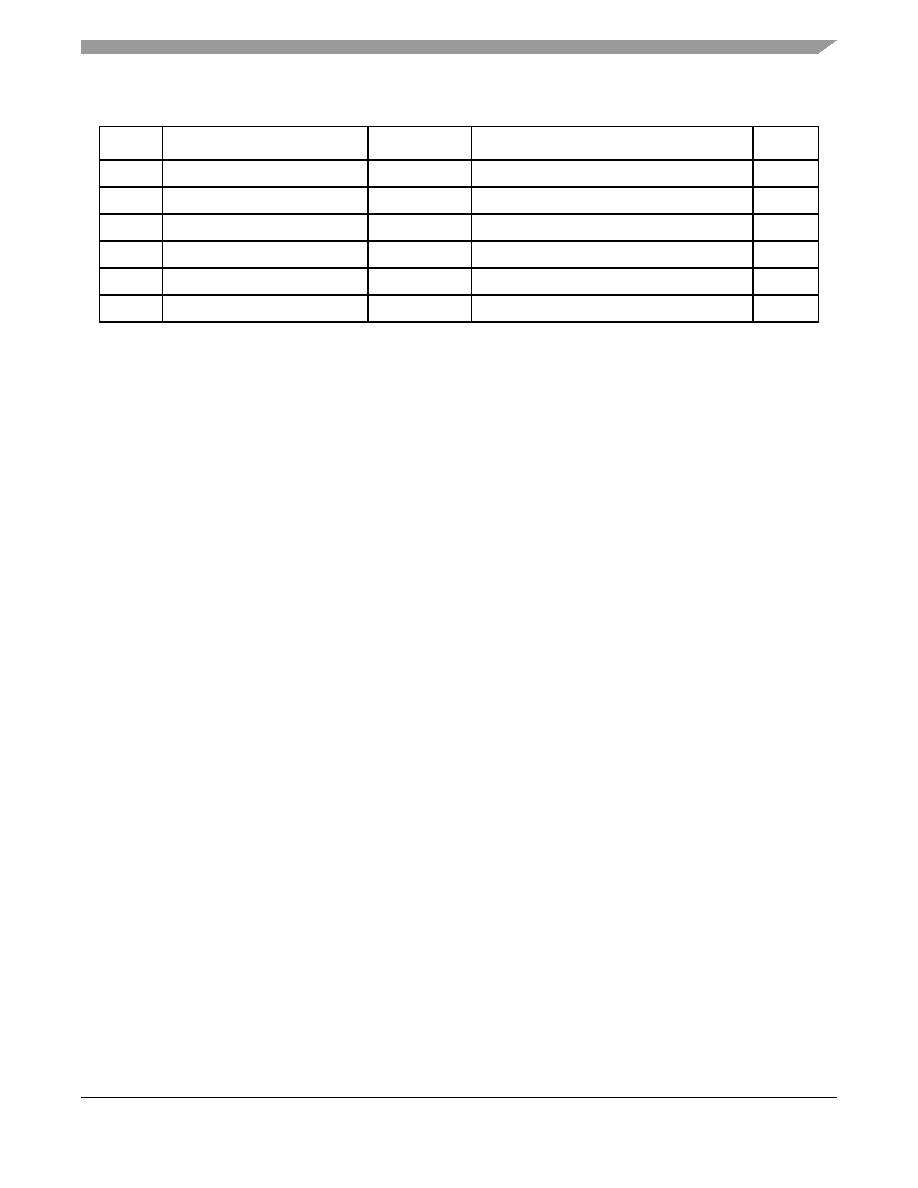

Table 46. Sharp Synchronous Display Interface Timing Parameters—Pixel Level

ID

Parameter

Symbol

Value

Units

IP21

SPL rise time

Tsplr

(BGXP – 1) * Tdpcp

ns

IP22

CLS rise time

Tclsr

CLS_RISE_DELAY * Tdpcp

ns

IP23

CLS fall time

Tclsf

CLS_FALL_DELAY * Tdpcp

ns

IP24

CLS rise and PS fall time

Tpsf

PS_FALL_DELAY * Tdpcp

ns

IP25

PS rise time

Tpsr

PS_RISE_DELAY * Tdpcp

ns

IP26

REV toggle time

Trev

REV_TOGGLE_DELAY * Tdpcp

ns

Because

of

an

order

from

the

United

States

International

Trade

Commission,

BGA-packaged

product

lines

and

part

numbers

indicated

here

currently

are

not

available

from

Freescale

for

import

or

sale

in

the

United

States

prior

to

September

2010:

MCIMX31CVMN4D,

MCIMX31LCVMN4D,

MCIMX31CVMN4C,

MCIMX31LCVMN4C

相关PDF资料 |

PDF描述 |

|---|---|

| MPC8545CHXATGB | 32-BIT, 1200 MHz, MICROPROCESSOR, CBGA783 |

| MPC8545ECHXAQGB | 32-BIT, 1000 MHz, MICROPROCESSOR, CBGA783 |

| MPC8547EVUAUJB | 32-BIT, 1000 MHz, MICROPROCESSOR, CBGA783 |

| MPC8548CVTAUJA | 32-BIT, 1333 MHz, MICROPROCESSOR, PBGA783 |

| MPC8548ECPXAVJ | 32-BIT, 1500 MHz, MICROPROCESSOR, PBGA783 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MCIMX31LCVMN4CR2 | 功能描述:处理器 - 专门应用 TORTOLA MX31 AUTO FULL RoHS:否 制造商:Freescale Semiconductor 类型:Multimedia Applications 核心:ARM Cortex A9 处理器系列:i.MX6 数据总线宽度:32 bit 最大时钟频率:1 GHz 指令/数据缓存: 数据 RAM 大小:128 KB 数据 ROM 大小: 工作电源电压: 最大工作温度:+ 95 C 安装风格:SMD/SMT 封装 / 箱体:MAPBGA-432 |

| MCIMX31LCVMN4D | 功能描述:处理器 - 专门应用 2.0.1 AUTO LITE RoHS:否 制造商:Freescale Semiconductor 类型:Multimedia Applications 核心:ARM Cortex A9 处理器系列:i.MX6 数据总线宽度:32 bit 最大时钟频率:1 GHz 指令/数据缓存: 数据 RAM 大小:128 KB 数据 ROM 大小: 工作电源电压: 最大工作温度:+ 95 C 安装风格:SMD/SMT 封装 / 箱体:MAPBGA-432 |

| MCIMX31LCVMN4DR2 | 功能描述:处理器 - 专门应用 2.0.1 AUTO LITE RoHS:否 制造商:Freescale Semiconductor 类型:Multimedia Applications 核心:ARM Cortex A9 处理器系列:i.MX6 数据总线宽度:32 bit 最大时钟频率:1 GHz 指令/数据缓存: 数据 RAM 大小:128 KB 数据 ROM 大小: 工作电源电压: 最大工作温度:+ 95 C 安装风格:SMD/SMT 封装 / 箱体:MAPBGA-432 |

| MCIMX31LDVKN5D | 功能描述:处理器 - 专门应用 2.0.1 CONSUMER LITE RoHS:否 制造商:Freescale Semiconductor 类型:Multimedia Applications 核心:ARM Cortex A9 处理器系列:i.MX6 数据总线宽度:32 bit 最大时钟频率:1 GHz 指令/数据缓存: 数据 RAM 大小:128 KB 数据 ROM 大小: 工作电源电压: 最大工作温度:+ 95 C 安装风格:SMD/SMT 封装 / 箱体:MAPBGA-432 |

| MCIMX31LDVKN5DR2 | 功能描述:处理器 - 专门应用 2.0.1 CONSUMER LITE RoHS:否 制造商:Freescale Semiconductor 类型:Multimedia Applications 核心:ARM Cortex A9 处理器系列:i.MX6 数据总线宽度:32 bit 最大时钟频率:1 GHz 指令/数据缓存: 数据 RAM 大小:128 KB 数据 ROM 大小: 工作电源电压: 最大工作温度:+ 95 C 安装风格:SMD/SMT 封装 / 箱体:MAPBGA-432 |

发布紧急采购,3分钟左右您将得到回复。