- 您现在的位置:买卖IC网 > PDF目录9191 > MPC92433AE (IDT, Integrated Device Technology Inc)IC SYNTHESIZER LVPECL 48-LQFP PDF资料下载

参数资料

| 型号: | MPC92433AE |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 5/21页 |

| 文件大小: | 0K |

| 描述: | IC SYNTHESIZER LVPECL 48-LQFP |

| 标准包装: | 250 |

| 类型: | 时钟/频率合成器 |

| PLL: | 带旁路 |

| 输入: | LVCMOS,晶体 |

| 输出: | LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 3:2 |

| 差分 - 输入:输出: | 无/是 |

| 频率 - 最大: | 1.428GHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-LQFP |

| 供应商设备封装: | 48-TQFP(7x7) |

| 包装: | 托盘 |

| 其它名称: | 800-2267 MPC92433AE-ND |

MPC92433 Data Sheet

1428MHZ DUAL OUTPUT LVPECL CLOCK SYNTHESIZER

MPC92433 REVISION 3 FEBRUARY 6, 2013

13

2013 Integrated Device Technology, Inc.

LOCK Detect

The LOCK detect circuitry indicates the frequency-lock status

of the PLL by setting and resetting the pin LOCK and register bit

LOCK simultaneously. After acquiring an internal frequency lock

state, the assertion of the LOCK signal is delayed at least 256

reference clock cycles to prevent signaling temporary PLL locks

during frequency transitions. The LOCK signal is deasserted

when the PLL lost lock, for instance when the reference clock is

removed: the LOCK signal goes low after missing at least two fref

clock cycles (NREF(UNLOCK)). The PLL may also lose lock when

the PLL feedback-divider M or pre-divider P is changed or the

DEC/INC command is issued. The PLL may not lose lock as a

result of slow reference frequency changes. In any case of losing

LOCK, the PLL attempts to re-lock to the reference frequency.

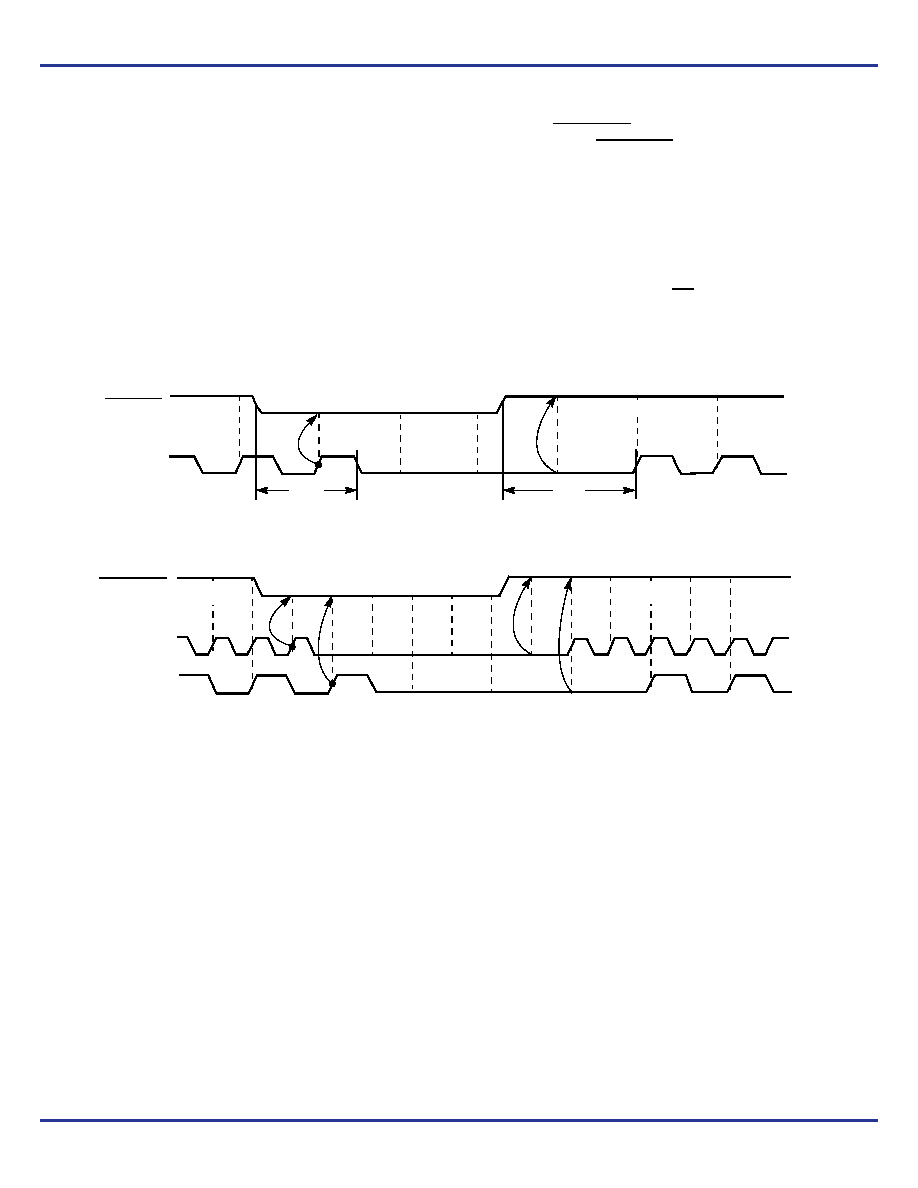

Output Clock Stop

Asserting CLK_STOPx will stop the respective output clock in

logic low state. The CLK_STOPx control is internally

synchronized to the output clock signal, therefore, enabling

and disabling outputs does not produce runt pulses. See

Figure 5.The clock stop controls of the QA and QB outputs are

independent on each other. If the QB runs at half of the QA output

frequency and both outputs are enabled at the same time, the first

clock pulse of QA may not appear at the same time of the first QB

output. (See Figure 6.) Concident rising edges of QA and QB stay

synchronous after the assertion and de-assertion of the

CLK_STOPx controls. Asserting MR always resets the output

divider to a logic low output state, with the risk of producing an

output runt pulse.

Figure 5. Clock Stop Timing for NB = 0 (fQA = fQB)

Figure 6. Clock Stop Timing for NB = 1 (fQA = 2 fQB)

CLK_STOPx

Qx

(Disable)

(Enable)

tP_DIS

tP_EN

CLK_STOPA,B

QA

QB

(Disable)

(Enable)

相关PDF资料 |

PDF描述 |

|---|---|

| VI-B1B-MY-F1 | CONVERTER MOD DC/DC 95V 50W |

| X9258TV24Z-2.7 | IC XDCP QUAD 256TP 100K 24TSSOP |

| VI-B1B-MW-F4 | CONVERTER MOD DC/DC 95V 100W |

| VI-B1B-MW-F2 | CONVERTER MOD DC/DC 95V 100W |

| X9250UV24IZ | IC XDCP QUAD 256TP 50K 24-TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MPC92433AER2 | 功能描述:时钟合成器/抖动清除器 FSL 1428MHz Dual Out put LVPECL Clock Syn RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

| MPC92439 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:900MHz, Low Voltage, LVPECL Clock Syntheesizer |

| MPC92439AC | 功能描述:IC SYNTHESIZER LVPECL 32-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| MPC92439ACR2 | 功能描述:IC SYNTHESIZER LVPECL 32-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| MPC92439EI | 功能描述:时钟合成器/抖动清除器 FSL 900MHz LVPECL Freq. Synthesizer RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。