- 您现在的位置:买卖IC网 > PDF目录363350 > NM24W16UFLZVN (FAIRCHILD SEMICONDUCTOR CORP) 16K-Bit Serial EEPROM 2-Wire Bus Interface PDF资料下载

参数资料

| 型号: | NM24W16UFLZVN |

| 厂商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分类: | PROM |

| 英文描述: | 16K-Bit Serial EEPROM 2-Wire Bus Interface |

| 中文描述: | 2K X 8 I2C/2-WIRE SERIAL EEPROM, PDIP8 |

| 封装: | PLASTIC, DIP-8 |

| 文件页数: | 11/13页 |

| 文件大小: | 109K |

| 代理商: | NM24W16UFLZVN |

11

www.fairchildsemi.com

NM24C16U/17U Rev. B.1

N

S

T

O

P

A

C

K

NO

A

C

K

SLAVE

ADDRESS

A

C

K

A

C

K

S

T

A

R

T

S

T

A

R

T

WORD

ADDRESS

SLAVE

ADDRESS

Bus Activity:

Master

SDA Line

Bus Activity:

NM24C16U/17U

DATA n

S

T

O

P

A

C

K

Bus Activity:

Master

SDA Line

Bus Activity:

NM24C16U/17U

A

C

K

DATA n + x

A

C

K

DATA n + 2

DATA n +1

DATA n +1

A

C

K

NO

A

C

K

Slave

Address

DS800010-18

DS800010-19

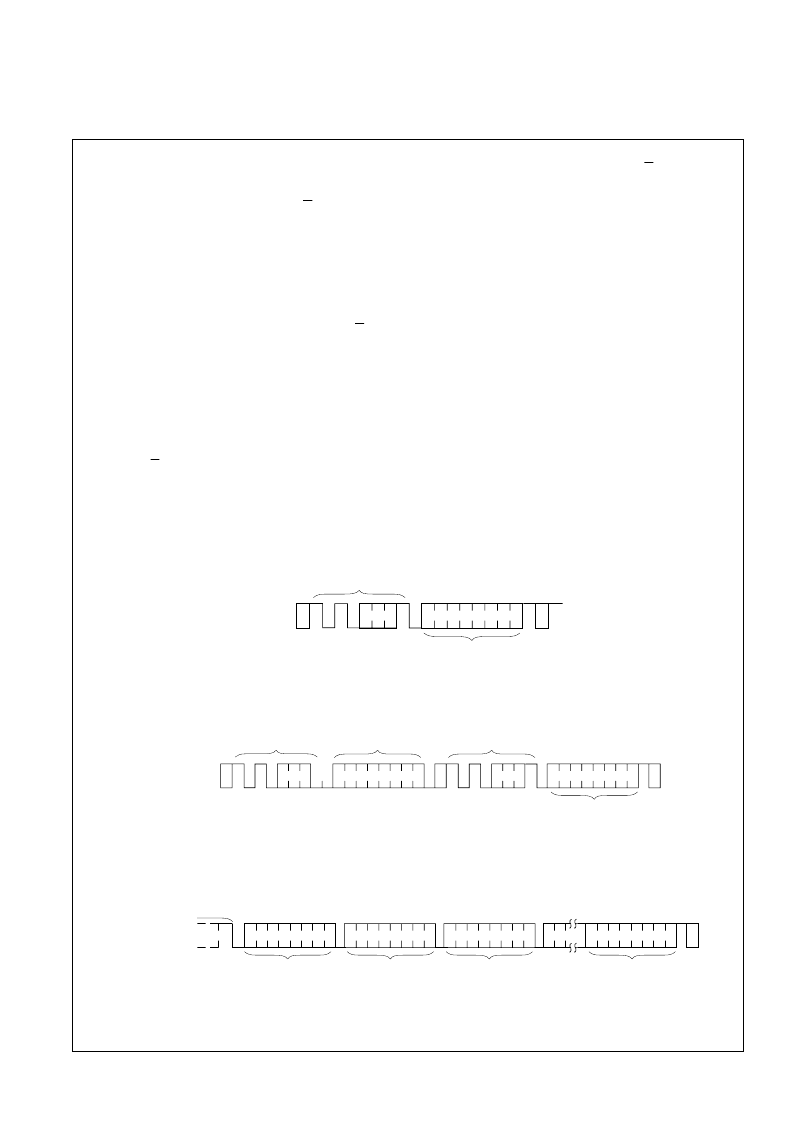

Read Operations

Read operations are initiated in the same manner as write

operations, with the exception that the R/W bit of the slave

address is set to a one. There are three basic read operations:

current address read, random read, and sequential read.

Current Address Read

Internally the NM24C16U/17U contains an address counter that

maintains the address of the last byte accessed, incremented by

one. Therefore, if the last access (either a read or write) was to

address n, the next read operation would access data from

address n + 1. Upon receipt of the slave address with R/W set to

one, the NM24C16U/17U issues an acknowledge and transmits

the eight bit byte. The master will not acknowledge the transfer

but does generate a stop condition, and therefore the NM24C16U/

17U discontinues transmission. Refer to Figure 8 for the se-

quence of address, acknowledge and data transfer.

Random Read

Random read operations allow the master to access any memory

location in a random manner. Prior to issuing the slave address

with the R/W bit set to one, the master must first perform a

“

dummy

”

write operation. The master issues the start condition,

slave address and then the byte address it is to read. After the

byte address acknowledge, the master immediately reissues the

start condition and the slave address with the R/W bit set to one.

This will be followed by an acknowledge from the NM24C16U/17U

and then by the eight bit data. The master will not acknowledge the

transfer but does generate the stop condition, and therefore the

NM24C16U/17U discontinues transmission. Refer to Figure 9 or

the address, acknowledge and data transfer sequence.

Sequential Read

Sequential reads can be initiated as either a current address read

or random access read. The first word is transmitted in the same

manner as the other read modes; however, the master now

responds with an acknowledge, indicating it requires additional

data. The NM24C16U/17U continues to output data for each

acknowledge received. The read operation is terminated by the

master not responding with an acknowledge or by generating a

stop condition.

The data output is sequential, with the data from address n

followed by the data from n + 1. The address counter for read

operations increments all word address bits, allowing the entire

memory contents to be serially read during one operation. After

the entire memory has been read, the counter "rolls over" and the

NM24C16U/17U continues to output data for each acknowledge

received. Refer to Figure 10for the address, acknowledge, and

data transfer sequence.

Current Address Read (Figure 8)

S

T

O

P

DATA

A

C

K

NO

A

C

K

S

T

A

R

T

SLAVE

ADDRESS

Bus Activity:

Master

SDA Line

Bus Activity:

NM24C16U/17U

DS800010-17

Random Read (Figure 9)

Sequential Read (Figure 10)

相关PDF资料 |

PDF描述 |

|---|---|

| NM24W16UFTMT8 | 16K-Bit Serial EEPROM 2-Wire Bus Interface |

| NM24W16UFTN | 16K-Bit Serial EEPROM 2-Wire Bus Interface |

| NM24W16UFTVM8 | 16K-Bit Serial EEPROM 2-Wire Bus Interface |

| NM24W16UFTVMT8 | 16K-Bit Serial EEPROM 2-Wire Bus Interface |

| NM24W16UFTVN | 16K-Bit Serial EEPROM 2-Wire Bus Interface |

相关代理商/技术参数 |

参数描述 |

|---|---|

| NM-250 | 制造商:WALDOM ELECTRONICS 功能描述: |

| NM-250-0015P | 制造商:WALDOM ELECTRONICS 功能描述: |

| NM-250-0025P | 制造商:WALDOM ELECTRONICS 功能描述: |

| NM25001S00 | 制造商:RadiSys 功能描述:LVDS;ADDCARD;BG845&LS855 |

| NM25C020 | 制造商:FAIRCHILD 制造商全称:Fairchild Semiconductor 功能描述:2K-Bit Serial CMOS EEPROM (Serial Peripheral Interface (SPI) Synchronous Bus) |

发布紧急采购,3分钟左右您将得到回复。