- 您现在的位置:买卖IC网 > PDF目录365666 > SN74V3650-6PEU (Texas Instruments, Inc.) 3.3-V CMOS FIRST-IN, FIRST-OUT MEMORIES PDF资料下载

参数资料

| 型号: | SN74V3650-6PEU |

| 厂商: | Texas Instruments, Inc. |

| 英文描述: | 3.3-V CMOS FIRST-IN, FIRST-OUT MEMORIES |

| 中文描述: | 的3.3V的CMOS先入先出存储器 |

| 文件页数: | 15/50页 |

| 文件大小: | 729K |

| 代理商: | SN74V3650-6PEU |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页

SN74V3640, SN74V3650, SN74V3660, SN74V3670, SN74V3680, SN74V3690

1024

×

36, 2048

×

36, 4096

×

36, 8192

×

36, 16384

×

36, 32768

×

36

3.3-V CMOS FIRST-IN, FIRST-OUT MEMORIES

SCAS668A

–

NOVEMBER 2001

–

REVISED MARCH 2003

15

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

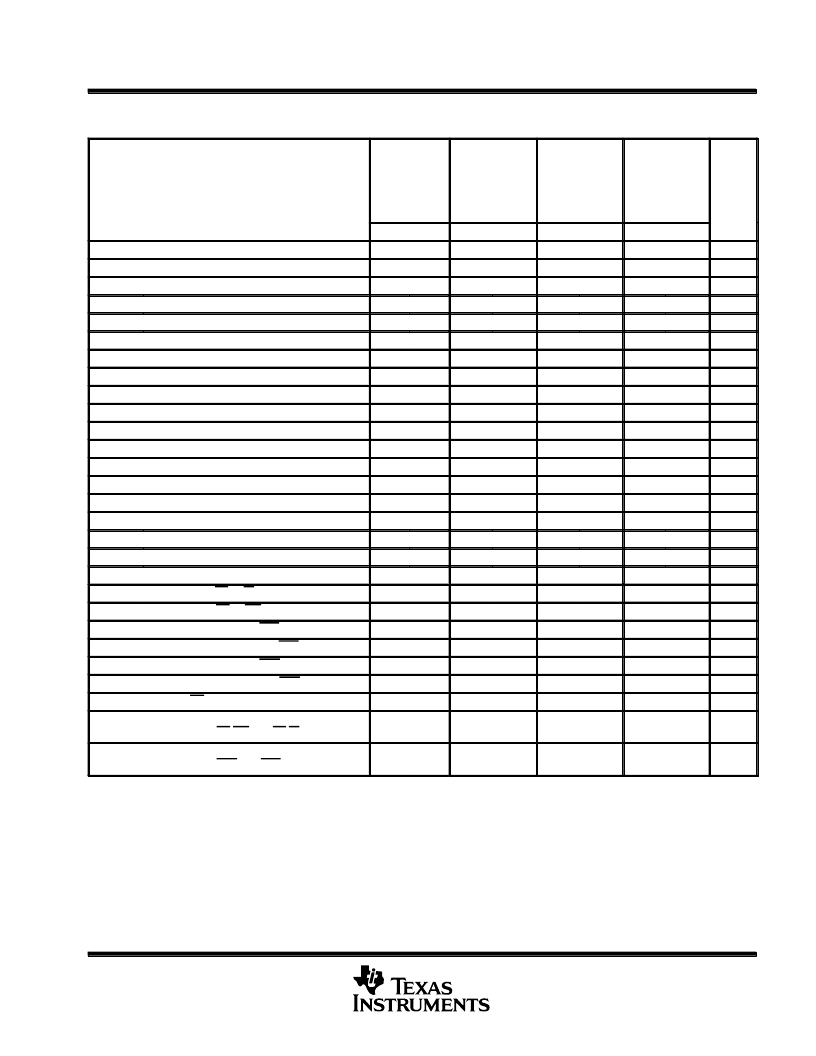

timing requirements over recommended ranges of supply voltage and operating free-air

temperature (see Figure 2 through Figure 22)

SN74V3640-6

SN74V3650-6

SN74V3660-6

SN74V3670-6

SN74V3680-6

SN74V3690-6

SN74V3640-7

SN74V3650-7

SN74V3660-7

SN74V3670-7

SN74V3680-7

SN74V3690-7

SN74V3640-10

SN74V3650-10

SN74V3660-10

SN74V3670-10

SN74V3680-10

SN74V3690-10

SN74V3640-15

SN74V3650-15

SN74V3660-15

SN74V3670-15

SN74V3680-15

SN74V3690-15

UNIT

MIN

MAX

MIN

MAX

MIN

MAX

MIN

MAX

fclock

tA

tCLK

tCLKH

tCLKL

tDS

tDH

tENS

tENH

tLDS

tLDH

tRS

tRSS

tRSR

tRSF

tRTS

tOLZ

tOE

tOHZ

tWFF

tREF

tPAFA

tPAFS

tPAEA

tPAES

tHF

Clock cycle frequency

166

133.3

100

66.7

MHz

Data access time

2

4.5

2

5

2

6.5

2

10

ns

Clock cycle time

6

7.5

10

15

ns

Clock high time

2.5

3.5

4.5

6

ns

Clock low time

2.5

3.5

4.5

6

ns

Data setup time

1.5

2.5

3.5

4

ns

Data hold time

0.5

0.5

0.5

1

ns

Enable setup time

1.5

2.5

3.5

4

ns

Enable hold time

0.5

0.5

0.5

1

ns

Load setup time

2

3.5

3.5

4

ns

Load hold time

Reset pulse duration

0

0.5

0.5

1

ns

10

10

10

15

ns

Reset setup time

15

15

15

15

ns

Reset recovery time

10

10

10

15

ns

Reset to flag and output time

15

15

15

15

ns

Retransmit setup time

2

3.5

3.5

4

ns

Output enable to output in low impedance

0

0

0

0

ns

Output enable to output valid

2

4.5

2

6

2

6

2

8

ns

Output enable to output in high impedance

2

4.5

2

6

2

6

2

8

ns

Write clock to FF or IR

4.5

5

6.5

10

ns

Read clock to EF or OR

4.5

5

6.5

10

ns

Clock to asynchronous PAF

8.5

12.5

16

20

ns

Write clock to synchronous PAF

4.5

5

6.5

10

ns

Clock to asynchronous PAE

8.5

12.5

16

20

ns

Read clock to synchronous PAE

4.5

5

6.5

10

ns

Clock to HF

9

12.5

16

20

ns

tsk1

Skew time between read clock and

write clock for EF/OR and FF/IR

4.5

5

7

9

ns

tsk2

Skew time between read clock and

write clock for PAE and PAF

All ac timings apply to standard mode and FWFT mode.

Pulse durations less than minimum values are not allowed.

4.5

7

10

14

ns

相关PDF资料 |

PDF描述 |

|---|---|

| SN74V3660-10PEU | 3.3-V CMOS FIRST-IN, FIRST-OUT MEMORIES |

| SN74V3660-15PEU | 3.3-V CMOS FIRST-IN, FIRST-OUT MEMORIES |

| SN74V3670-10PEU | 3.3-V CMOS FIRST-IN, FIRST-OUT MEMORIES |

| SN74V3670-15PEU | 3.3-V CMOS FIRST-IN, FIRST-OUT MEMORIES |

| SN74V3690-15PEU | 3.3-V CMOS FIRST-IN, FIRST-OUT MEMORIES |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SN74V3650-7PEU | 功能描述:先进先出 2048 x 36 Synch 先进先出 Memory RoHS:否 制造商:IDT 电路数量: 数据总线宽度:18 bit 总线定向:Unidirectional 存储容量:4 Mbit 定时类型:Synchronous 组织:256 K x 18 最大时钟频率:100 MHz 访问时间:10 ns 电源电压-最大:3.6 V 电源电压-最小:6 V 最大工作电流:35 mA 最大工作温度:+ 85 C 封装 / 箱体:TQFP-80 封装: |

| SN74V3660-10PEU | 功能描述:先进先出 4096 x 36 Synch 先进先出 Memory RoHS:否 制造商:IDT 电路数量: 数据总线宽度:18 bit 总线定向:Unidirectional 存储容量:4 Mbit 定时类型:Synchronous 组织:256 K x 18 最大时钟频率:100 MHz 访问时间:10 ns 电源电压-最大:3.6 V 电源电压-最小:6 V 最大工作电流:35 mA 最大工作温度:+ 85 C 封装 / 箱体:TQFP-80 封装: |

| SN74V3660-15PEU | 功能描述:先进先出 4096 x 36 Synch 先进先出 Memory RoHS:否 制造商:IDT 电路数量: 数据总线宽度:18 bit 总线定向:Unidirectional 存储容量:4 Mbit 定时类型:Synchronous 组织:256 K x 18 最大时钟频率:100 MHz 访问时间:10 ns 电源电压-最大:3.6 V 电源电压-最小:6 V 最大工作电流:35 mA 最大工作温度:+ 85 C 封装 / 箱体:TQFP-80 封装: |

| SN74V3660-6PEU | 功能描述:先进先出 4096 x 36 Synch 先进先出 Memory RoHS:否 制造商:IDT 电路数量: 数据总线宽度:18 bit 总线定向:Unidirectional 存储容量:4 Mbit 定时类型:Synchronous 组织:256 K x 18 最大时钟频率:100 MHz 访问时间:10 ns 电源电压-最大:3.6 V 电源电压-最小:6 V 最大工作电流:35 mA 最大工作温度:+ 85 C 封装 / 箱体:TQFP-80 封装: |

| SN74V3660-7PEU | 功能描述:先进先出 4096 x 36 Synch 先进先出 Memory RoHS:否 制造商:IDT 电路数量: 数据总线宽度:18 bit 总线定向:Unidirectional 存储容量:4 Mbit 定时类型:Synchronous 组织:256 K x 18 最大时钟频率:100 MHz 访问时间:10 ns 电源电压-最大:3.6 V 电源电压-最小:6 V 最大工作电流:35 mA 最大工作温度:+ 85 C 封装 / 箱体:TQFP-80 封装: |

发布紧急采购,3分钟左右您将得到回复。