- 您现在的位置:买卖IC网 > PDF目录365666 > SN74V3650-6PEU (Texas Instruments, Inc.) 3.3-V CMOS FIRST-IN, FIRST-OUT MEMORIES PDF资料下载

参数资料

| 型号: | SN74V3650-6PEU |

| 厂商: | Texas Instruments, Inc. |

| 英文描述: | 3.3-V CMOS FIRST-IN, FIRST-OUT MEMORIES |

| 中文描述: | 的3.3V的CMOS先入先出存储器 |

| 文件页数: | 21/50页 |

| 文件大小: | 729K |

| 代理商: | SN74V3650-6PEU |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页当前第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页

SN74V3640, SN74V3650, SN74V3660, SN74V3670, SN74V3680, SN74V3690

1024

×

36, 2048

×

36, 4096

×

36, 8192

×

36, 16384

×

36, 32768

×

36

3.3-V CMOS FIRST-IN, FIRST-OUT MEMORIES

SCAS668A

–

NOVEMBER 2001

–

REVISED MARCH 2003

21

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

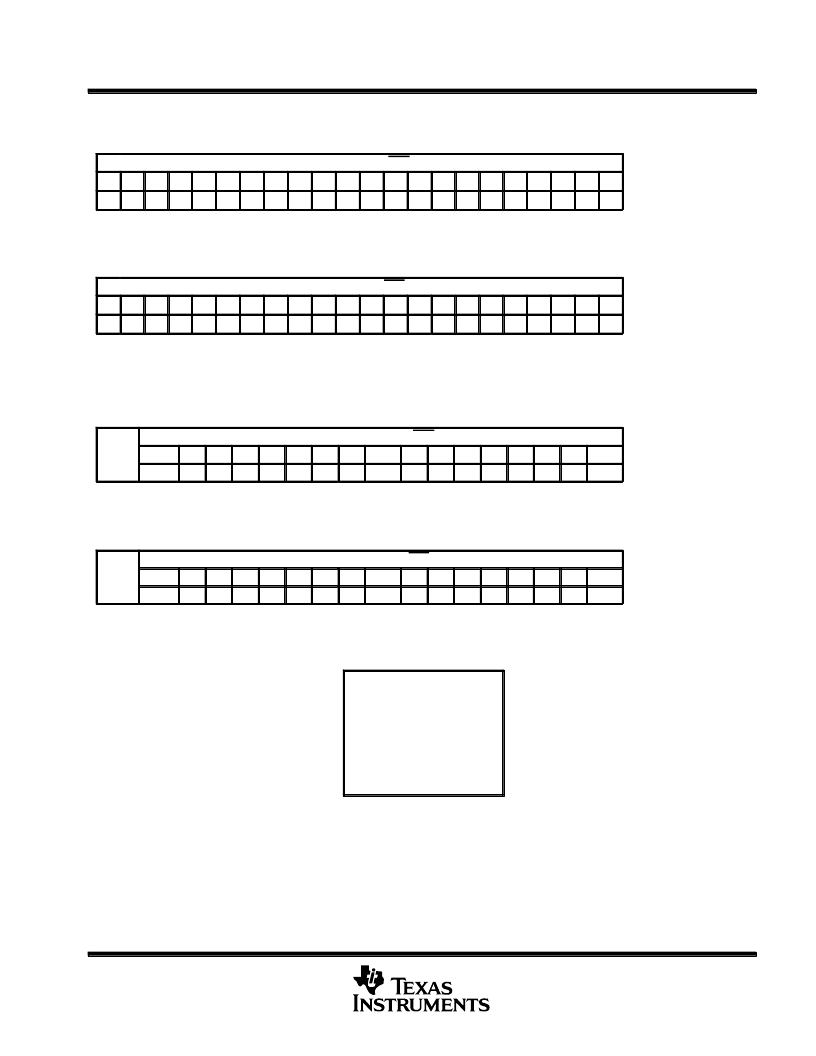

1st Parallel Offset Write/Read Cycle

Data Inputs/Outputs

D/Q35

D/Q15

D/Q8

D/Q0

EMPTY OFFSET REGISTER (PAE) BIT LOCATIONS

X

X

X

X

X

X

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

Noninterspersed Parity

X

X

X

X

X

15

14

13

12

11

10

9

X

8

7

6

5

4

3

2

1

Interspersed Parity

2nd Parallel Offset Write/Read Cycle

Data Inputs/Outputs

D/Q35

D/Q17

D/Q8

D/Q0

FULL OFFSET REGISTER (PAF) BIT LOCATIONS

X

X

X

X

X

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

Noninterspersed Parity

X

X

X

X

16

15

14

13

12

11

10

9

X

8

7

6

5

4

3

2

1

Interspersed Parity

×

36 Bus Width

1st Parallel Offset Write/Read Cycle

D/Q17

D/Q15

Data Inputs/Outputs

D/Q0

EMPTY OFFSET (LSB) REGISTER (PAE) BIT LOCATIONS

14

13

12

11

10

9

X

X

X

15

8

7

6

5

4

3

2

1

Noninterspersed Parity

Interspersed Parity

X

15

14

13

12

11

10

9

X

8

7

6

5

4

3

2

1

D/Q8

2nd Parallel Offset Write/Read Cycle

D/Q17

D/Q15

Data Inputs/Outputs

D/Q0

FULL OFFSET (LSB) REGISTER (PAF) BIT LOCATIONS

14

13

12

11

10

X

X

X

15

9

8

7

6

5

4

3

2

1

Noninterspersed Parity

X

15

14

13

12

11

10

9

X

8

7

6

5

4

3

2

1

Interspersed Parity

D/Q8

×

18 Bus Width

Number of bits used:

10 bits for the SN74V3640

11 bits for the SN74V3650

12 bits for the SN74V3660

13 bits for the SN74V3670

14 bits for the SN74V3680

15 bits for the SN74V3690

Note: All unused bits of the

LSB and MSB are don

’

t care.

Figure 3. Programmable Flag Offset Programming Sequence (Continued)

Figure 1Figure 2

相关PDF资料 |

PDF描述 |

|---|---|

| SN74V3660-10PEU | 3.3-V CMOS FIRST-IN, FIRST-OUT MEMORIES |

| SN74V3660-15PEU | 3.3-V CMOS FIRST-IN, FIRST-OUT MEMORIES |

| SN74V3670-10PEU | 3.3-V CMOS FIRST-IN, FIRST-OUT MEMORIES |

| SN74V3670-15PEU | 3.3-V CMOS FIRST-IN, FIRST-OUT MEMORIES |

| SN74V3690-15PEU | 3.3-V CMOS FIRST-IN, FIRST-OUT MEMORIES |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SN74V3650-7PEU | 功能描述:先进先出 2048 x 36 Synch 先进先出 Memory RoHS:否 制造商:IDT 电路数量: 数据总线宽度:18 bit 总线定向:Unidirectional 存储容量:4 Mbit 定时类型:Synchronous 组织:256 K x 18 最大时钟频率:100 MHz 访问时间:10 ns 电源电压-最大:3.6 V 电源电压-最小:6 V 最大工作电流:35 mA 最大工作温度:+ 85 C 封装 / 箱体:TQFP-80 封装: |

| SN74V3660-10PEU | 功能描述:先进先出 4096 x 36 Synch 先进先出 Memory RoHS:否 制造商:IDT 电路数量: 数据总线宽度:18 bit 总线定向:Unidirectional 存储容量:4 Mbit 定时类型:Synchronous 组织:256 K x 18 最大时钟频率:100 MHz 访问时间:10 ns 电源电压-最大:3.6 V 电源电压-最小:6 V 最大工作电流:35 mA 最大工作温度:+ 85 C 封装 / 箱体:TQFP-80 封装: |

| SN74V3660-15PEU | 功能描述:先进先出 4096 x 36 Synch 先进先出 Memory RoHS:否 制造商:IDT 电路数量: 数据总线宽度:18 bit 总线定向:Unidirectional 存储容量:4 Mbit 定时类型:Synchronous 组织:256 K x 18 最大时钟频率:100 MHz 访问时间:10 ns 电源电压-最大:3.6 V 电源电压-最小:6 V 最大工作电流:35 mA 最大工作温度:+ 85 C 封装 / 箱体:TQFP-80 封装: |

| SN74V3660-6PEU | 功能描述:先进先出 4096 x 36 Synch 先进先出 Memory RoHS:否 制造商:IDT 电路数量: 数据总线宽度:18 bit 总线定向:Unidirectional 存储容量:4 Mbit 定时类型:Synchronous 组织:256 K x 18 最大时钟频率:100 MHz 访问时间:10 ns 电源电压-最大:3.6 V 电源电压-最小:6 V 最大工作电流:35 mA 最大工作温度:+ 85 C 封装 / 箱体:TQFP-80 封装: |

| SN74V3660-7PEU | 功能描述:先进先出 4096 x 36 Synch 先进先出 Memory RoHS:否 制造商:IDT 电路数量: 数据总线宽度:18 bit 总线定向:Unidirectional 存储容量:4 Mbit 定时类型:Synchronous 组织:256 K x 18 最大时钟频率:100 MHz 访问时间:10 ns 电源电压-最大:3.6 V 电源电压-最小:6 V 最大工作电流:35 mA 最大工作温度:+ 85 C 封装 / 箱体:TQFP-80 封装: |

发布紧急采购,3分钟左右您将得到回复。