- 您现在的位置:买卖IC网 > PDF目录69376 > ST7FLITE10BY0M6 (STMICROELECTRONICS) 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PDSO16 PDF资料下载

参数资料

| 型号: | ST7FLITE10BY0M6 |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PDSO16 |

| 封装: | 0.300 INCH, ROHS COMPLIANT, PLASTIC, SOP-16 |

| 文件页数: | 76/159页 |

| 文件大小: | 2855K |

| 代理商: | ST7FLITE10BY0M6 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页当前第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页

ST7LITE1xB

23/159

7 SUPPLY, RESET AND CLOCK MANAGEMENT

The device includes a range of utility features for

securing the application in critical situations (for

example in case of a power brown-out), and re-

ducing the number of external components.

Main features

■ Clock Management

– 1 MHz internal RC oscillator (enabled by op-

tion byte, available on ST7LITE15B and

ST7LITE19B devices only)

– 1 to 16 MHz External crystal/ceramic resona-

tor (selected by option byte)

– External Clock Input (enabled by option byte)

– PLL for multiplying the frequency by 8 or 4

(enabled by option byte)

– For clock ART counter only: PLL32 for multi-

plying the 8 MHz frequency by 4 (enabled by

option byte). The 8 MHz input frequency is

mandatory and can be obtained in the follow-

ing ways:

–1 MHz RC + PLLx8

–16 MHz external clock (internally divided

by 2)

–2 MHz. external clock (internally divided by

2) + PLLx8

–Crystal oscillator with 16 MHz output fre-

quency (internally divided by 2)

■ Reset Sequence Manager (RSM)

■ System Integrity Management (SI)

– Main supply Low voltage detection (LVD) with

reset generation (enabled by option byte)

– Auxiliary Voltage detector (AVD) with interrupt

capability for monitoring the main supply (en-

abled by option byte)

7.1 INTERNAL RC OSCILLATOR ADJUSTMENT

The device contains an internal RC oscillator with

an accuracy of 1% for a given device, temperature

and voltage range (4.5V-5.5V). It must be calibrat-

ed to obtain the frequency required in the applica-

tion. This is done by software writing a 10-bit cali-

bration value in the RCCR (RC Control Register)

and in the bits 6:5 in the SICSR (SI Control Status

Register).

Whenever the microcontroller is reset, the RCCR

returns to its default value (FFh), i.e. each time the

device is reset, the calibration value must be load-

ed in the RCCR. Predefined calibration values are

stored in EEPROM for 3 and 5V VDD supply volt-

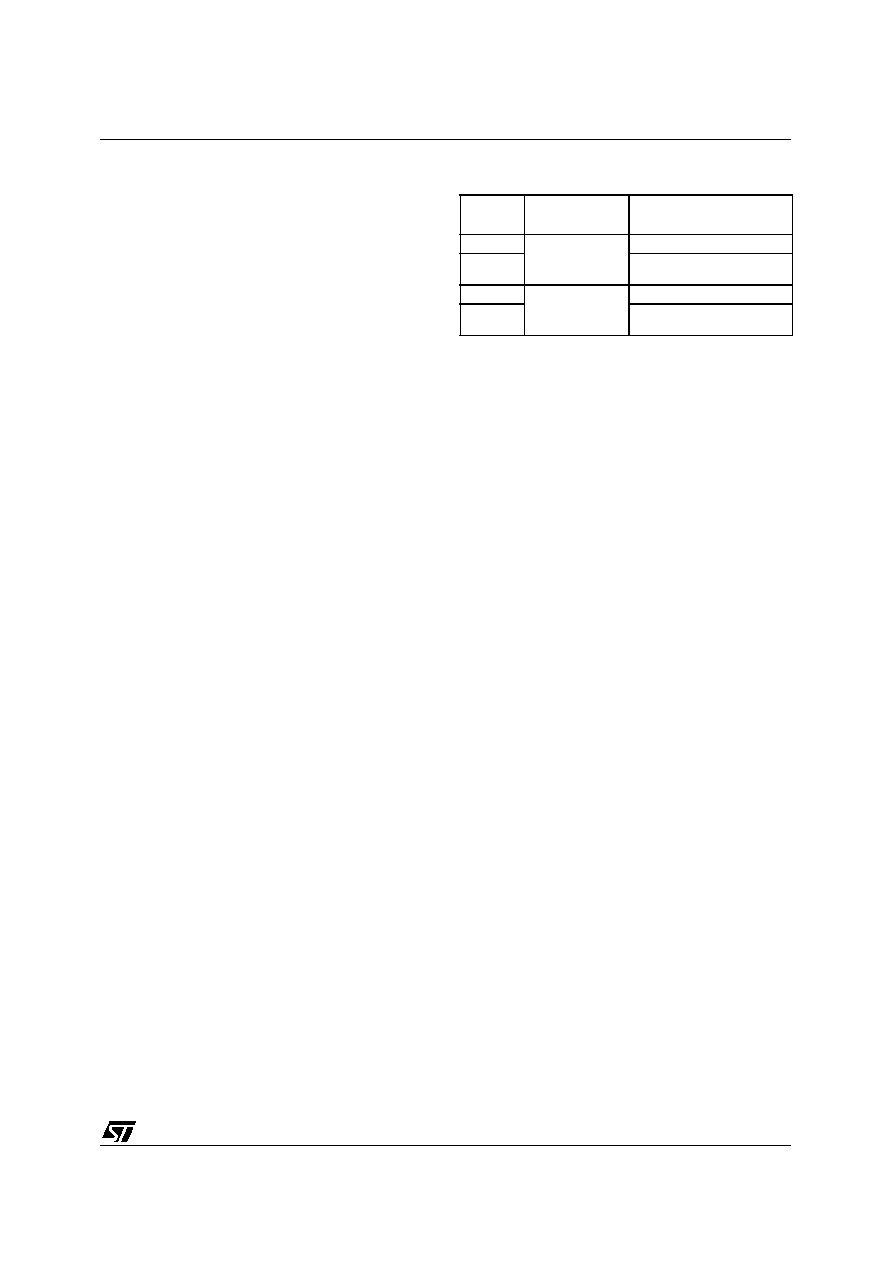

ages at 25°C, as shown in the following table.

1. DEE0h, DEE1h, DEE2h and DEE3h addresses

are located in a reserved area of non-volatile

memory. They are read-only bytes for the applica-

tion code. This area cannot be erased or pro-

grammed by any ICC operation.

For compatibility reasons with the SICSR register,

CR[1:0] bits are stored in the 5th and 6th position

of DEE1 and DEE3 addresses.

Notes:

– In 38-pulse ICC mode, the internal RC oscillator

is forced as a clock source, regardless of the se-

lection in the option byte. For ST7LITE10B devic-

es which do not support the internal RC

oscillator, the “option byte disabled” mode must

be used (35-pulse ICC mode entry, clock provid-

ed by the tool).

page 110. for more information on the frequency

and accuracy of the RC oscillator.

– To improve clock stability and frequency accura-

cy, it is recommended to place a decoupling ca-

pacitor, typically 100nF, between the VDD and

VSS pins as close as possible to the ST7 device.

– These bytes are systematically programmed by

ST, including on FASTROM devices.

Caution: If the voltage or temperature conditions

change in the application, the frequency may need

to be recalibrated.

Refer to application note AN1324 for information

on how to calibrate the RC frequency using an ex-

ternal reference signal.

7.2 PHASE LOCKED LOOP

The PLL can be used to multiply a 1MHz frequen-

cy from the RC oscillator or the external clock by 4

or 8 to obtain fOSC of 4 or 8 MHz. The PLL is ena-

bled and the multiplication factor of 4 or 8 is select-

ed by 2 option bits.

– The x4 PLL is intended for operation with VDD in

the 2.7V to 3.3V range

RCCR

Conditions

ST7LITE1xB

Address

RCCRH0 VDD=5V

TA=25°C

fRC=1MHz

DEE0h 1) (CR[9:2])

RCCRL0

DEE1h 1) (CR[1:0])

RCCRH1 VDD=3.3V

TA=25°C

fRC=1MHz

DEE2h 1) (CR[9:2])

RCCRL1

DEE3h 1) (CR[1:0])

1

相关PDF资料 |

PDF描述 |

|---|---|

| ST7FLITE10BY1M3TR | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PDSO16 |

| ST7FLITE10BY1M6 | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PDSO16 |

| ST7FLITE19BF0M3TR | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PDSO20 |

| ST7FLITE19BF0M3 | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PDSO20 |

| ST7FLITE19BF0U3 | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PQCC20 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST7FLITE10F1B6 | 功能描述:8位微控制器 -MCU Flash 4K SPI RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| ST7FLITE10F1B6 | 制造商:STMicroelectronics 功能描述:IC 8BIT FLASH MCU 7FLITE10 DIP20 |

| ST7FLITE10F1M6 | 功能描述:8位微控制器 -MCU Flash 4K SPI RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| ST7FLITE15 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT MCU WITH SINGLE VOLTAGE FLASH MEMORY, DATA EEPROM, ADC, 4 TIMERS, SPI |

| ST7FLITE15F1B6 | 功能描述:8位微控制器 -MCU Flash 4K SPI RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

发布紧急采购,3分钟左右您将得到回复。