- 您现在的位置:买卖IC网 > PDF目录69378 > ST7PL38F2MC/XXXE (STMICROELECTRONICS) 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO20 PDF资料下载

参数资料

| 型号: | ST7PL38F2MC/XXXE |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO20 |

| 封装: | 0.300 INCH, ROHS COMPLIANT, PLASTIC, SOP-20 |

| 文件页数: | 166/168页 |

| 文件大小: | 2955K |

| 代理商: | ST7PL38F2MC/XXXE |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页当前第166页第167页第168页

Obsolete

Product(s)

- Obsolete

Product(s)

ST7L34, ST7L35, ST7L38, ST7L39

97/168

LINSCI

SERIAL COMMUNICATION INTERFACE (SCI Mode) (cont’d)

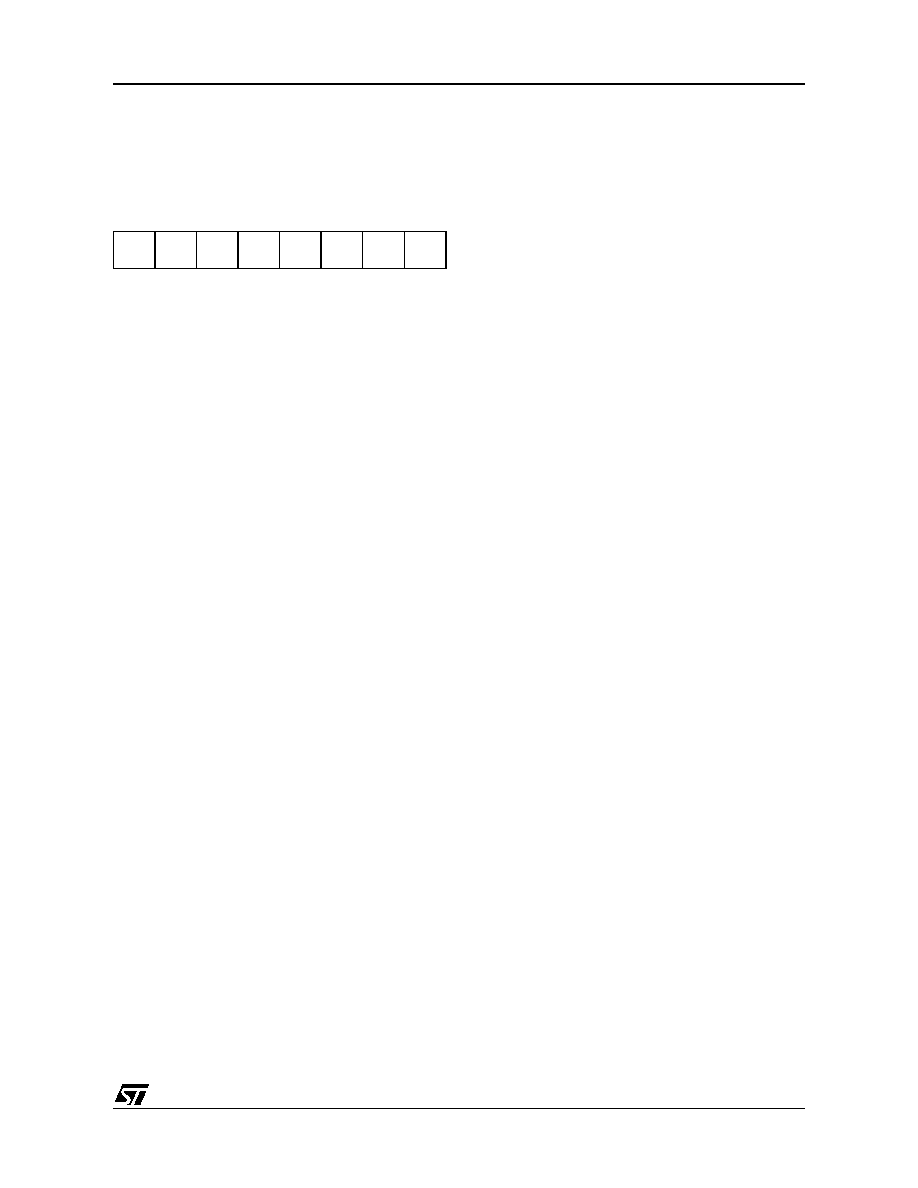

CONTROL REGISTER 1 (SCICR1)

Read/Write

Reset Value: x000 0000 (x0h)

1)This bit has a different function in LIN mode, please

refer to the LIN mode register description.

Bit 7 = R8 Receive data bit 8

This bit is used to store the 9th bit of the received

word when M = 1.

Bit 6 = T8 Transmit data bit 8

This bit is used to store the 9th bit of the transmit-

ted word when M = 1.

Bit 5 = SCID Disabled for low power consumption

When this bit is set the SCI prescalers and outputs

are stopped and the end of the current byte trans-

fer in order to reduce power consumption.This bit

is set and cleared by software.

0: SCI enabled

1: SCI prescaler and outputs disabled

Bit 4 = M Word length

This bit determines the word length. It is set or

cleared by software.

0: 1 Start bit, 8 Data bits, 1 Stop bit

1: 1 Start bit, 9 Data bits, 1 Stop bit

Note: The M bit must not be modified during a data

transfer (both transmission and reception).

Bit 3 = WAKE Wake-Up method

This bit determines the SCI Wake-Up method, it is

set or cleared by software.

0: Idle Line

1: Address Mark

Note: If the LINE bit is set, the WAKE bit is deacti-

vated and replaced by the LHDM bit.

Bit 2 = PCE Parity control enable

This bit is set and cleared by software. It selects

the hardware parity control (generation and detec-

tion for byte parity, detection only for LIN parity).

0: Parity control disabled

1: Parity control enabled

Bit 1 = PS Parity selection

This bit selects the odd or even parity when the

parity generation/detection is enabled (PCE bit

set). It is set and cleared by software. The parity

will be selected after the current byte.

0: Even parity

1: Odd parity

Bit 0 = PIE Parity interrupt enable

This bit enables the interrupt capability of the hard-

ware parity control when a parity error is detected

(PE bit set). The parity error involved can be a byte

parity error (if bit PCE is set and bit LPE is reset) or

a LIN parity error (if bit PCE is set and bit LPE is

set).

0: Parity error interrupt disabled

1: Parity error interrupt enabled

70

R8

T8

SCID

M

WAKE PCE1)

PS

PIE

1

相关PDF资料 |

PDF描述 |

|---|---|

| ST7PL38F2UCXXXRE | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, QCC20 |

| ST7PL39F2MA/XXXE | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO20 |

| ST7L38F2UC/XXXE | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, QCC20 |

| ST7FL38F2UATRE | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, QCC20 |

| ST7PL35F2MAXXXRE | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO20 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST7PLITE02F0U6TR | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT MICROCONTROLLER WITH SINGLE VOLTAGE FLASH MEMORY, DATA EEPROM, ADC, TIMERS, SPI |

| ST7PLITE02Y0B6 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT MICROCONTROLLER WITH SINGLE VOLTAGE FLASH MEMORY, DATA EEPROM, ADC, TIMERS, SPI |

| ST7PLITE02Y0B6TR | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-bit microcontroller with single voltage Flash memory, data EEPROM, ADC, timers, SPI |

| ST7PLITE02Y0M6 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-bit microcontroller with single voltage Flash memory, data EEPROM, ADC, timers, SPI |

| ST7PLITE02Y0M6TR | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-bit microcontroller with single voltage Flash memory, data EEPROM, ADC, timers, SPI |

发布紧急采购,3分钟左右您将得到回复。