参数资料

| 型号: | SY87739LHG |

| 厂商: | Micrel Inc |

| 文件页数: | 15/17页 |

| 文件大小: | 0K |

| 描述: | IC SYNTHESIZER FRACT 3.3V 32TQFP |

| 标准包装: | 250 |

| 系列: | AnyClock® |

| 类型: | 分数合成器 |

| PLL: | 是 |

| 主要目的: | 以太网,光纤通道,SONET/SDH/ATM |

| 输入: | PECL |

| 输出: | PECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:1 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 729MHz |

| 电源电压: | 3.15 V ~ 3.45 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-TQFP 裸露焊盘 |

| 供应商设备封装: | 32-EPAD-TQFP |

| 包装: | 托盘 |

| 其它名称: | 576-1407 |

Micrel, Inc.

SY87739L

June 2011

7

M9999-061511

hbwhelp@micrel.com

Functional Description

General

The SY87739L AnyClock Fractional-N Synthesizer is

used in serial data streaming applications, where the

incoming data rate on a channel may vary, or where the

incoming data rate on a channel is unknown ahead of

time.

In these situations, a valid output stream must still be

generated even in the absence of any edges on the

corresponding input stream. Up until now, designers had

to resort to sub-optimal solutions such as providing

multiple reference oscillators. Beyond the potential noise

and EMI issues, the designer has no way to future proof

his circuit, as it would prove near impossible to pre-

provision all the reference frequencies that might be

needed after deployment, yet are unknown at this time.

The SY87739L solves this problem by generating exact

frequencies for common data streaming protocols, all

from one 27MHz reference. If any of these protocols

include overhead due to use of common digital

wrappers, The SY87739L still generates the exact

frequency required, including the overhead.

Besides

generating

reference

rates

for

common

protocols

directly,

the

SY87739L

also

generates

reference frequencies for Micrel’s SY87721L CDR/CMU,

such that it will reliably recover data at any rate between

28Mbps and 2,700Mbps without any gaps.

A simple 3-wire MicroWire bit-serial interface loads a

configuration that describes the desired output reference

frequency. All common microcontrollers support this

MicroWire interface. Those microcontrollers that don’t

support this interface in hardware can easily emulate the

interface in firmware.

The large set of possible frequencies that the SY87739L

generates, are divided into three classes. First, the sets

of frequencies that match a particular data streaming

protocol are in the “protocol” category. Second, the set

of frequencies that are guaranteed to be near enough to

any arbitrary data rate such that the SY87721L will lock

are in the “picket fence” category. Third, the set of

frequencies that do not fit into either of the first two

categories is in the third category.

The SY87739L generates these important reference

frequencies through two tandem PLL circuits. The first

PLL uses a modified fractional-N approach to generate a

rational

ratio

frequency.

This

PLL

is

capable

of

generating all protocol data rates, except for those that

include FEC or digital wrapper overhead. A second,

more traditional P/Q synthesizer optionally adjusts the

output frequency of the first, fractional-N synthesizer, to

accommodate these FEC or digital wrapper data rates.

The bit serial interface conveys 32 bits of configuration

data from a microcontroller to SY87739L. This simple

interface consists of an active high chip select, a serial

clock (2MHz or less) and a serial data input. Each clock

cycle

one

bit

of

configuration

data

transfers

to

SY87739L.

Circuit Description

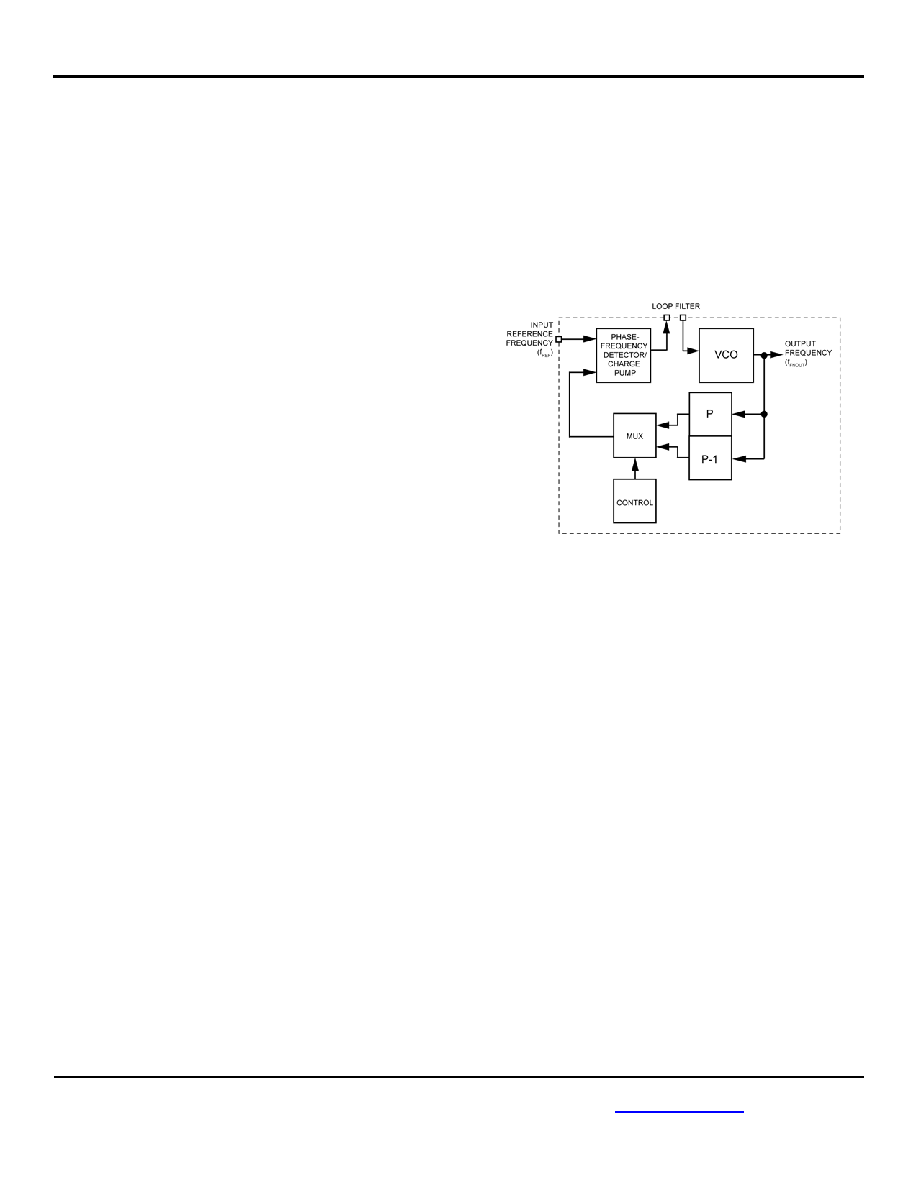

The heart of SY87739L is its fractional-N synthesizer, as

shown in Figure 1.

Figure 1. Fractional-N Synthesizer Architecture

The two dividers in the feedback path always differ by

one count. That is, if one divider is set to divide by P = 5,

then the other divider divides by P–1 = 4. The mux

chooses between the two based on the control circuit.

The idea behind the fractional-N approach is that every

input reference edge is used. Only those output edges

that are nearest to an input edge get fed back to the

phase-frequency comparator. In addition, the nearest

output edges are chosen in such a way that the net

offset, over a number of edges, zeroes out. It is the

control circuit’s job to drive the mux such that only the

“correct” edges get fed back.

In the above fractional-N circuit, if the output frequency

should be, for example, 5 times the input frequency, then

P is set to 5, and the control circuit sets the mux to only

feed back the output of the P divider.

If the output frequency should be, for example, 41/2

times the input frequency, then the control circuit

alternates evenly between the P and the P–1 divider

output. For every two input edges (one to compare

against P, and another to compare against P–1), you will

get 5 + 4 output edges, yielding an output frequency 9/2

the input frequency.

or (408) 955-1690

相关PDF资料 |

PDF描述 |

|---|---|

| SY87813LHG | IC CLOCK/DATA REC 1.3GBPS 32TQFP |

| SY89295UTI TR | IC DELAY LINE 1024TAP 32-TQFP |

| SY89296UTI TR | IC DELAY LINE 1024TAP 32-TQFP |

| SY89297UMH TR | IC DELAY LINE 1024TAP 2NS 24-MLF |

| SY897132LKY TR | IC LINK REPLICATOR 28TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SY87739LHI | 功能描述:IC SYNTHESIZER FRACT 3.3V 32TQFP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:AnyClock® 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| SY87739LHITR | 制造商:MICREL 制造商全称:Micrel Semiconductor 功能描述:PROTOCOL TRANSPARENT 3.3V 10MHz to 729MHz FRACTIONAL-N SYNTHESIZER |

| SY87739LHY | 功能描述:时钟合成器/抖动清除器 3.3V Fractional N Synthesizer (10MHz to 729MHz) (Lead Free/I Temp/32 pin TQFP) RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

| SY87739LHY TR | 功能描述:时钟合成器/抖动清除器 3.3V Fractional N Synthesizer (10MHz to 729MHz) (Lead Free/I Temp/32 pin TQFP) RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

| SY87739LHYTR | 制造商:MICREL 制造商全称:Micrel Semiconductor 功能描述:PROTOCOL TRANSPARENT 3.3V 10MHz to 729MHz FRACTIONAL-N SYNTHESIZER |

发布紧急采购,3分钟左右您将得到回复。