- 您现在的位置:买卖IC网 > PDF目录382635 > TMS320C6454ZTZ (Texas Instruments, Inc.) Fixed-Point Digital Signal Processor PDF资料下载

参数资料

| 型号: | TMS320C6454ZTZ |

| 厂商: | Texas Instruments, Inc. |

| 元件分类: | 数字信号处理 |

| 英文描述: | Fixed-Point Digital Signal Processor |

| 中文描述: | 定点数字信号处理器 |

| 文件页数: | 34/225页 |

| 文件大小: | 1663K |

| 代理商: | TMS320C6454ZTZ |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页当前第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页第190页第191页第192页第193页第194页第195页第196页第197页第198页第199页第200页第201页第202页第203页第204页第205页第206页第207页第208页第209页第210页第211页第212页第213页第214页第215页第216页第217页第218页第219页第220页第221页第222页第223页第224页第225页

www.ti.com

P

TMS320C6454

Fixed-Point Digital Signal Processor

SPRS311A–APRIL 2006–REVISED DECEMBER 2006

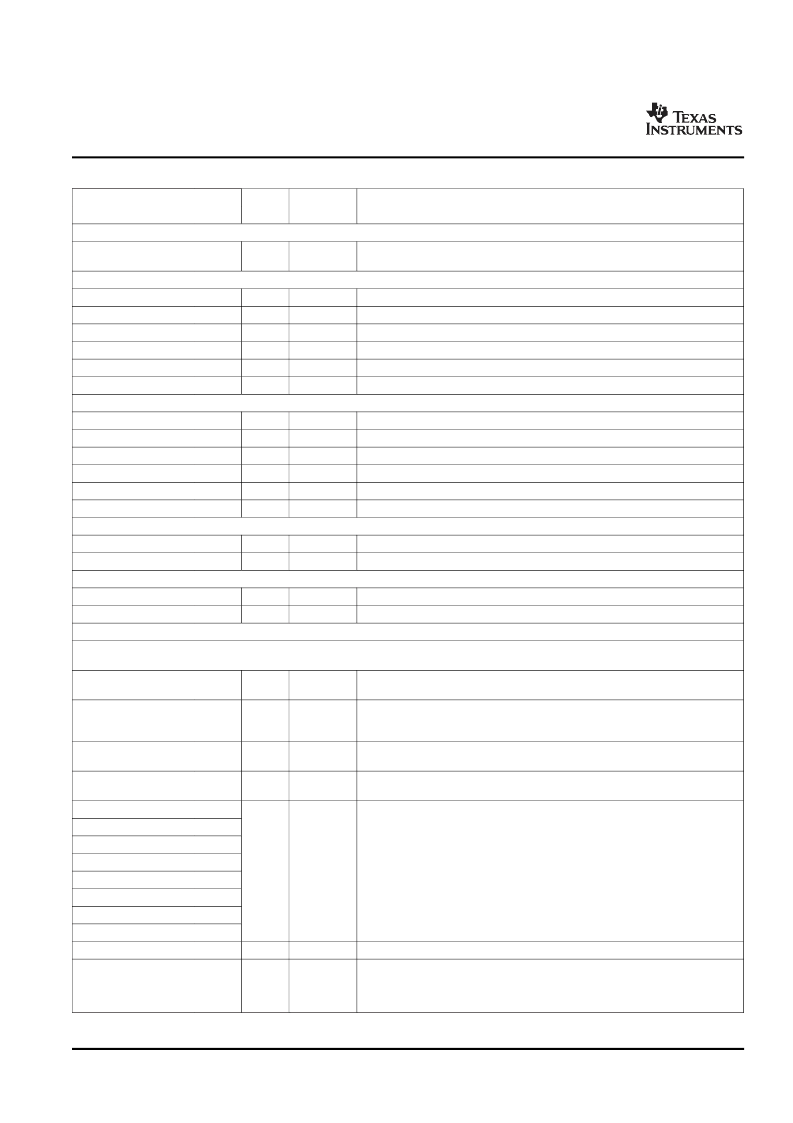

Table 2-3. Terminal Functions (continued)

SIGNAL

NAME

MULTICHANNEL BUFFERED SERIAL PORT 1 AND MULTICHANNEL BUFFERED SERIAL PORT 0 (McBSP1 and McBSP0)

McBSP external clock source (as opposed to internal) (

I

)

CLKS

AJ4

I

IPD

[shared by McBSP1 and McBSP0]

MULTICHANNEL BUFFERED SERIAL PORT 1 (McBSP1)

CLKR1/GP[0]

AF4

I/O/Z

IPD

McBSP1 receive clock (

I/O/Z

) or GP[0] (

I/O/Z

) [default]

FSR1/GP[10]

AE5

I/O/Z

IPD

McBSP1 receive frame sync (

I/O/Z

) or GP[10] (

I/O/Z

)[default]

DR1/GP[8]

AH5

I/O/Z

IPD

McBSP1 receive data (

I

) or GP[8] (

I/O/Z

) [default]

DX1/GP[9]

AG5

I/O/Z

IPD

McBSP1 transmit data (

O/Z

) or GP[9] (

I/O/Z

) [default]

FSX1/GP[11]

AG4

I/O/Z

IPD

McBSP1 transmit frame sync (

I/O/Z

) or GP[11] (

I/O/Z

) [default]

CLKX1/GP[3]

AF5

I/O/Z

IPD

McBSP1 transmit clock (

I/O/Z

) or GP[3] (

I/O/Z

) [default]

MULTICHANNEL BUFFERED SERIAL PORT 0 (McBSP0)

CLKR0

AG1

I/O/Z

IPU

McBSP0 receive clock (

I/O/Z

)

FSR0

AH3

I/O/Z

IPD

McBSP0 receive frame sync (

I/O/Z

)

DR0

AJ5

I

IPD

McBSP0 receive data (

I

)

DX0

AF6

I/O/Z

IPD

McBSP0 transmit data (

O/Z

)

FSX0

AJ3

I/O/Z

IPD

McBSP0 transmit frame sync (

I/O/Z

)

CLKX0

AG6

I/O/Z

IPU

McBSP0 transmit clock (

I/O/Z

)

MANAGEMENT DATA INPUT/OUTPUT (MDIO) FOR MII/RMII/GMII

MDCLK

M5

I/O/Z

IPD

MDIO serial clock (MDCLK) for MII/RMII/RGMII mode (

O

)

MDIO

N3

I/O/Z

IPU

MDIO serial data (MDIO) for MII/RMII/RGMII mode (

I/O

)

MANAGEMENT DATA INPUT/OUTPUT (MDIO) FOR RGMII

RGMDCLK

B4

O/Z

MDIO serial clock for RGMII mode (RGMDCLK) (

O

)

RGMDIO

A4

I/O/Z

MDIO serial data for RGMII mode (RGMDIO) (

I/O

)

ETHERNET MAC (EMAC) [MII/RMII/GMII]

There are two configuration pins — the MAC_SEL[1:0] (AEA[10:9] pins) that select one of the four interface modes (MII, RMII, GMII, or

RGMII) for the EMAC/MDIO interface. For more detailed information on the EMAC configuration pins, see

Section 3

,

Device Configuration

.

This pin is EMAC receive clock (MRCLK) for MII [default] or GMII.

MRCLK

H1

I

MACSEL[1:0] dependent.

This pin is EMAC carrier sense (MCRS) (

I

) for MII [default] or GMII, or EMAC

MCRS/RMCRSDV

J4

I/O/Z

carrier sense/receive data valid (RMCRSDV) (

I

) for RMII. MACSEL[1:0]

dependent.

This pin is EMAC receive error (MRXIR) (

I

) for MII [default], RMII, or GMII.

MRXER/RMRXER

H4

I

MACSEL[1:0] dependent.

This pin is EMAC MII [default] or GMII receive data valid (MRXDV) (

I

).

MRXDV

H5

I

MACSEL[1:0] dependent.

MRXD7

M2

MRXD6

H2

MRXD5

L2

EMAC receive data bus for MII [default], RMII, or GMII

MRXD4

L1

I

These pins function as EMAC receive data pins for MII [default], RMII, or GMII

MRXD3

J3

(MRXD[x:0]) (

I

). MACSEL[1:0] dependent.

MRXD2

J1

MRXD1/RMRXD1

H3

MRXD0/RMRXD0

J2

GMTCLK

K5

O/Z

This pin is EMAC GMII transmit clock (GMTCLK) (

O

). MACSEL[1:0] dependent.

This pin is either EMAC MII [default] or GMII transmit clock (MTCLK) (

I

) or the

EMAC RMII reference clock (RMREFCLK) (

I

). The EMAC function is controlled

MTCLK/RMREFCLK

N4

I

by the MACSEL[1:0] (AEA[10:9] pins). For more detailed information, see

Section 3

,

Device Configuration

.

TYPE

(1)

IPD/IPU

(2)

DESCRIPTION

NO.

Device Overview

34

Submit Documentation Feedback

相关PDF资料 |

PDF描述 |

|---|---|

| TMS320C6454ZTZ7 | Fixed-Point Digital Signal Processor |

| TMS320C6454ZTZ8 | Fixed-Point Digital Signal Processor |

| TMX320C6454GTZ | Fixed-Point Digital Signal Processor |

| TMX320C6454GTZ7 | Fixed-Point Digital Signal Processor |

| TMX320C6454GTZ8 | Fixed-Point Digital Signal Processor |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TMS320C6454ZTZ7 | 制造商:TI 制造商全称:Texas Instruments 功能描述:Fixed-Point Digital Signal Processor |

| TMS320C6454ZTZ8 | 制造商:TI 制造商全称:Texas Instruments 功能描述:Fixed-Point Digital Signal Processor |

| TMS320C6455 | 制造商:TI 制造商全称:Texas Instruments 功能描述:Fixed-Point Digital Signal Processor |

| TMS320C6455_07 | 制造商:TI 制造商全称:Texas Instruments 功能描述:Fixed-Point Digital Signal Processor |

| TMS320C6455BCTZ | 功能描述:数字信号处理器和控制器 - DSP, DSC Fixed-Point Dig Sig Proc RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

发布紧急采购,3分钟左右您将得到回复。