- 您现在的位置:买卖IC网 > PDF目录376449 > X98021L128-3.3-Z (INTERSIL CORP) 210MHz Triple Video Digitizer with Digital PLL PDF资料下载

参数资料

| 型号: | X98021L128-3.3-Z |

| 厂商: | INTERSIL CORP |

| 元件分类: | 消费家电 |

| 英文描述: | 210MHz Triple Video Digitizer with Digital PLL |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP128 |

| 封装: | 14 X 20 MM, ROHS COMPLIANT, MS-022, MQFP-128 |

| 文件页数: | 19/29页 |

| 文件大小: | 294K |

| 代理商: | X98021L128-3.3-Z |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页

19

FN8219.0

June 2, 2005

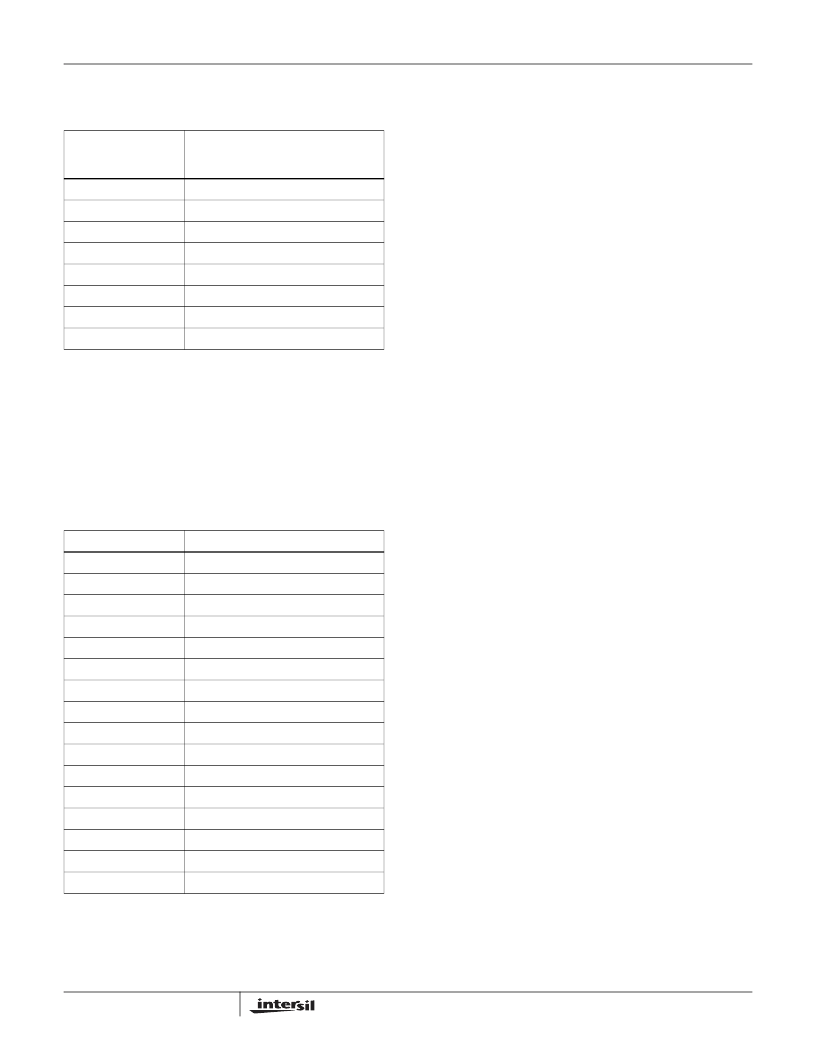

Table 3 shows the corner frequency for different register

settings.

Register 0x0D[7:4] controls a programmable zero, allowing

high frequencies to be boosted, restoring some of the

harmonics lost due to excessive EMI filtering, cable losses, etc.

This control has a very large range, and can introduce high

frequency noise into the image, so it should be used judiciously,

or as an advanced user adjustment.

Table 4 shows the corner frequency of the zero for different

peaking register settings.

Offset DAC

The X98021 features a 10 bit Digital-to-Analog Converter

(DAC) to provide extremely fine control over the full channel

offset. The DAC is placed after the PGA to eliminate

interaction between the PGA (controlling “contrast”) and the

Offset DAC (controlling “brightness”).

In normal operation, the Offset DAC is controlled by the

ABLC circuit, ensuring that the offset is always reduced

to sub-LSB levels (See the following ABLC section for

more information). When ABLC is enabled, the Offset

registers (0x09, 0x0A, 0x0B) control a digital offset added

to or subtracted from the output of the ADC. This mode

provides the best image quality and eliminates the need for

any offset calibration.

If desired, ABLC can be disabled (0x17[0]=1) and the

Offset DAC programmed manually, with the 8 most

significant bits in registers 0x09, 0x0A, 0x0B, and the 2 least

significant bits in register 0x0C[7:2].

The default Offset DAC range is ±127 ADC LSBs. Setting

0x0C[0]=1 reduces the swing of the Offset DAC by 50%,

making 1 Offset DAC LSB the weight of 1/8th of an ADC

LSB. This provides the finest offset control and applies to

both ABLC and manual modes.

Automatic Black Level Compensation (ABLC)

ABLC is a function that continuously removes all offset

errors from the incoming video signal by monitoring the

offset at the output of the ADC and servoing the 10 bit

analog DAC to force those errors to zero. When ABLC is

enabled, the user offset control is a digital adder, with 8 bit

resolution (See Table 5).

When the ABLC function is enabled (0x17[0]=0), the ABLC

function is executed every line after the trailing edge of

HSYNC. If register 0x05[5] = 0 (the default), the ABLC

function will not be triggered while the DPLL is coasting,

preventing any composite sync edges, equalization pulses,

or Macrovision signals from corrupting the black data and

potentially adding a small error in the ABLC accumulator.

After the trailing edge of HSYNC, the start of ABLC is delayed

by the number of pixels specified in registers 0x14 and 0x15.

After that delay, the number of pixels specified by register

0x17[3:2] are averaged together and added to the ABLC’s

accumulator. The accumulator stores the average black levels

for the number of lines specified by register 0x17[6:4], which

is then used to generate a 10 bit DAC value.

The default values provide excellent results with offset

stability and absolute accuracy better than 1 ADC LSB for

most input signals. Increasing the ABLC pixel width or the

ABLC bandwidth settings decreases the ABLC’s absolute

DC error further.

ADC

The X98021 features 3 fully differential, 210MSPS 8 bit

ADCs.

TABLE 3. BANDWIDTH CONTROL

0x0D[3:0] VALUE

(LSB = “x” =

“don’t care”)

AFE BANDWIDTH

000x

100MHz

001x

130MHz

010x

150MHz

011x

180MHz

100x

230MHz

101x

320MHz

110x

480MHz

111x

780MHz

TABLE 4. PEAKING CORNER FREQUENCIES

0X0D[7:4] VALUE

ZERO CORNER FREQUENCY

0x0

Peaking disabled

0x1

800MHz

0x2

400MHz

0x3

265MHz

0x4

200MHz

0x5

160MHz

0x6

135MHz

0x7

115MHz

0x8

100MHz

0x9

90MHz

0xA

80MHz

0xB

70MHz

0xC

65MHz

0xD

60MHz

0xE

55MHz

0xF

50MHz

X98021

相关PDF资料 |

PDF描述 |

|---|---|

| X98024 | 240MHz Triple Video Digitizer with Digital PLL |

| X98024L128-3.3 | 240MHz Triple Video Digitizer with Digital PLL |

| X98024L128-3.3-Z | 240MHz Triple Video Digitizer with Digital PLL |

| XC145481 | 3 V PCM Codec-Filter |

| XC145481DW | 3 V PCM Codec-Filter |

相关代理商/技术参数 |

参数描述 |

|---|---|

| X98024 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:240MHz Triple Video Digitizer with Digital PLL |

| X98024_06 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:240MHz Triple Video Digitizer with Digital PLL |

| X98024L128-3.3 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:240MHz Triple Video Digitizer with Digital PLL |

| X98024L128-3.3-Z | 功能描述:IC TRPL VID DIGITIZER 128MQFP RoHS:是 类别:集成电路 (IC) >> 线性 - 视频处理 系列:- 标准包装:250 系列:- 类型:电平移位器 应用:LCD 电视机/监控器 安装类型:表面贴装 封装/外壳:28-WFQFN 裸露焊盘 供应商设备封装:28-WQFN(4x4)裸露焊盘 包装:带卷 (TR) 其它名称:296-32523-2TPS65198RUYT-ND |

| X98027 | 制造商:XICOR 制造商全称:Xicor Inc. 功能描述:PRELIMINARY INFORMATION |

发布紧急采购,3分钟左右您将得到回复。