参数资料

| 型号: | 24AA014T-I/MS |

| 厂商: | Microchip Technology |

| 文件页数: | 3/36页 |

| 文件大小: | 0K |

| 描述: | IC EEPROM 1KBIT 400KHZ 8MSOP |

| 产品培训模块: | I2C Serial EEPROM |

| 标准包装: | 2,500 |

| 格式 - 存储器: | EEPROMs - 串行 |

| 存储器类型: | EEPROM |

| 存储容量: | 1K (128 x 8) |

| 速度: | 100kHz,400kHz |

| 接口: | I²C,2 线串口 |

| 电源电压: | 1.8 V ~ 5.5 V |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 8-TSSOP,8-MSOP(0.118",3.00mm 宽) |

| 供应商设备封装: | 8-MSOP |

| 包装: | 带卷 (TR) |

第1页第2页当前第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

�� �

�

�

�24AA014/24LC014�

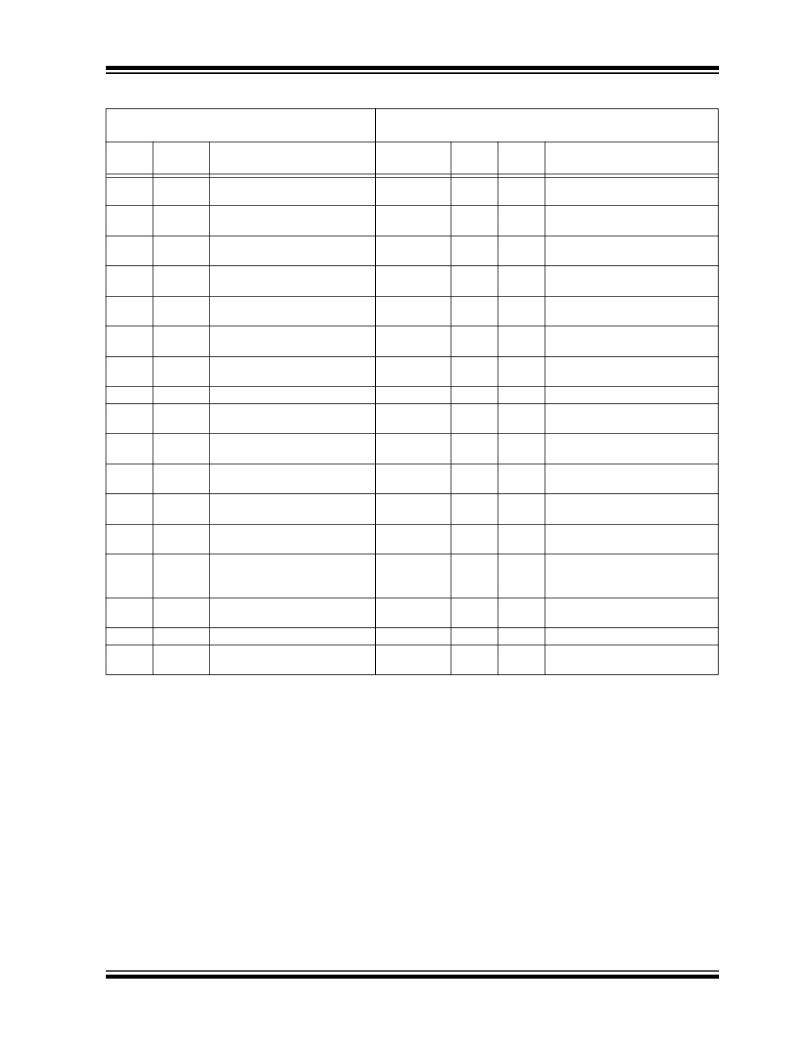

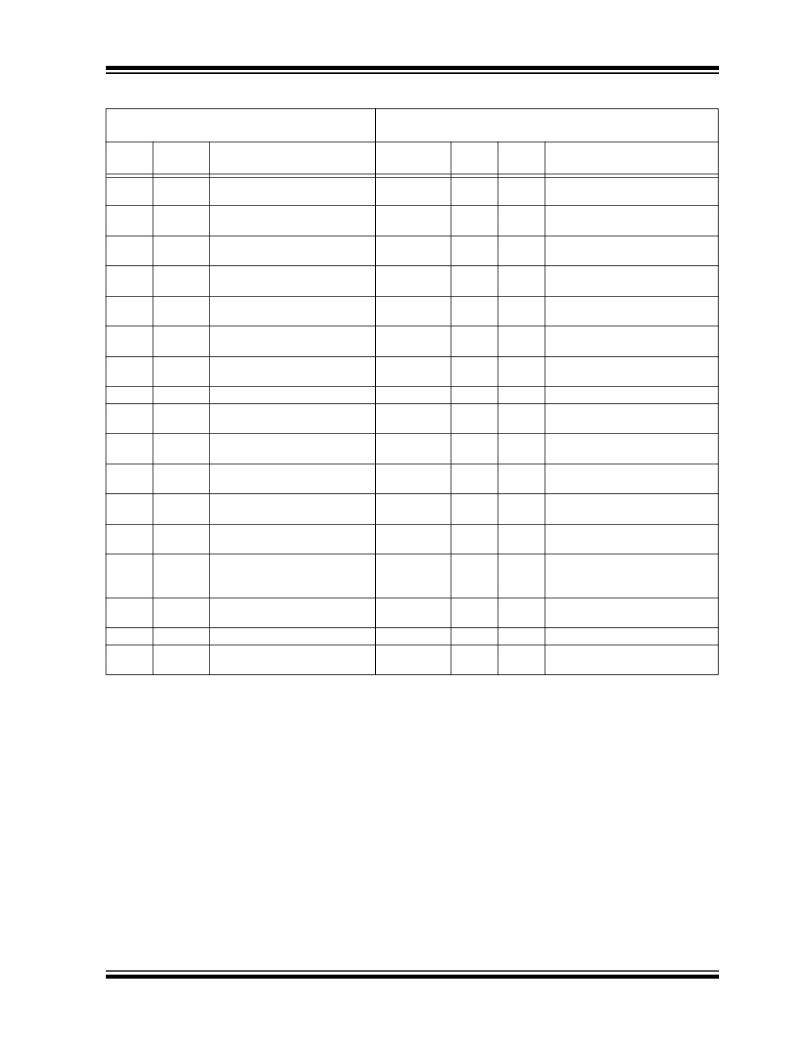

�TABLE� 1-2:�

�AC� CHARACTERISTICS�

�AC� CHARACTERISTICS�

�Industrial� (I):� T� A� =� -40°C� to� +85°C,� V� CC� =� +1.7V� to� +5.5V�

�Automotive� (E):� T� A� =� -40°C� to� +125°C,� V� CC� =� +2.5V� to� +5.5V�

�Param.�

�No.�

�1�

�Symbol�

�F� CLK�

�Characteristic�

�Clock� frequency�

�Min.�

�—�

�Max.�

�100�

�Units�

�kHz�

�Conditions�

�1.7V� ?� V� CC� <� 1.8V�

�—�

�400�

�1.8V� ?� V� CC� ?� 5.5V�

�2�

�T� HIGH�

�Clock� high� time�

�4000�

�—�

�ns�

�1.7V� ?� V� CC� <� 1.8V�

�600�

�—�

�1.8V� ?� V� CC� ?� 5.5V�

�3�

�T� LOW�

�Clock� low� time�

�4700�

�—�

�ns�

�1.7V� ?� V� CC� <� 1.8V�

�1300�

�—�

�1.8V� ?� V� CC� ?� 5.5V�

�4�

�T� R�

�SDA� and� SCL� rise� time� (� Note� 1� )�

�—�

�1000�

�ns�

�1.7V� ?� V� CC� <� 1.8V�

�—�

�300�

�1.8V� ?� V� CC� ?� 5.5V�

�5�

�T� F�

�SDA� and� SCL� fall� time� (� Note� 1� )�

�—�

�1000�

�ns�

�1.7V� ?� V� CC� <� 1.8V�

�—�

�300�

�1.8V� ?� V� CC� ?� 5.5V�

�6�

�T� HD� :� STA�

�Start� condition� hold� time�

�4000�

�—�

�ns�

�1.7V� ?� V� CC� <� 1.8V�

�600�

�—�

�1.8V� ?� V� CC� ?� 5.5V�

�7�

�T� SU� :� STA�

�Start� condition� setup� time�

�4700�

�—�

�ns�

�1.7V� ?� V� CC� <� 1.8V�

�600�

�—�

�1.8V� ?� V� CC� ?� 5.5V�

�8�

�9�

�T� HD� :� DAT�

�T� SU� :� DAT�

�Data� input� hold� time�

�Data� input� setup� time�

�0�

�250�

�—�

�—�

�ns�

�ns�

�(� Note� 2� )�

�1.7V� ?� V� CC� <� 1.8V�

�100�

�—�

�1.8V� ?� V� CC� ?� 5.5V�

�10�

�T� SU� :� STO�

�Stop� condition� setup� time�

�4000�

�—�

�ns�

�1.7V� ?� V� CC� <� 1.8V�

�600�

�—�

�1.8V� ?� V� CC� ?� 5.5V�

�11�

�T� SU� :� WP�

�WP� setup� time�

�4000�

�—�

�ns�

�1.7V� ?� V� CC� <� 1.8V�

�600�

�—�

�1.8V� ?� V� CC� ?� 5.5V�

�12�

�T� HD� :� WP�

�WP� hold� time�

�4700�

�—�

�ns�

�1.7V� ?� V� CC� <� 1.8V�

�600�

�—�

�1.8V� ?� V� CC� ?� 5.5V�

�13�

�T� AA�

�Output� valid� from� clock� (� Note� 2� )�

�—�

�3500�

�ns�

�1.7V� ?� V� CC� <� 1.8V�

�—�

�900�

�1.8V� ?� V� CC� ?� 5.5V�

�14�

�T� BUF�

�Bus� free� time:� Time� the� bus� must�

�4700�

�—�

�ns�

�1.7V� ?� V� CC� <� 1.8V�

�be� free� before� a� new� transmission�

�1300�

�—�

�1.8V� ?� V� CC� ?� 5.5V�

�can� start�

�16�

�T� SP�

�Input� filter� spike� suppression�

�—�

�50�

�ns�

�(� Note� 1� and� Note� 3� )�

�(SDA� and� SCL� pins)�

�17�

�18�

�T� WC�

�—�

�Write� cycle� time� (byte� or� page)�

�Endurance�

�—�

�1M�

�5�

�—�

�ms�

�cycles�

�—�

�25°C,� V� CC� =� 5.5V,� Block� mode�

�(� Note� 4� )�

�Note� 1:� Not� 100%� tested.� C� B� =� total� capacitance� of� one� bus� line� in� pF.�

�2:� As� a� transmitter,� the� device� must� provide� an� internal� minimum� delay� time� to� bridge� the� undefined� region� (minimum�

�300� ns)� of� the� falling� edge� of� SCL� to� avoid� unintended� generation� of� Start� or� Stop� conditions.�

�3:� The� combined� T� SP� and� V� HYS� specifications� are� due� to� new� Schmitt� Trigger� inputs,� which� provide� improved� noise� spike�

�suppression.� This� eliminates� the� need� for� a� T� I� specification� for� standard� operation.�

�4:� This� parameter� is� not� tested� but� ensured� by� characterization.� For� endurance� estimates� in� a� specific� application,� please�

�consult� the� Total� Endurance?� Model� which� can� be� obtained� from� Microchip’s� web� site� at� www.microchip.com.�

�?� 2010� Microchip� Technology� Inc.�

�DS21809G-page� 3�

�相关PDF资料 |

PDF描述 |

|---|---|

| FMC20DRYH-S734 | CONN EDGECARD 40POS DIP .100 SLD |

| 93LC46CX-E/SN | IC EEPROM 1KBIT 3MHZ 8SOIC |

| ASC40DRYI-S734 | CONN EDGECARD 80POS DIP .100 SLD |

| 93C46C-E/SN | IC EEPROM 1KBIT 3MHZ 8SOIC |

| EMC65DRTS-S13 | CONN EDGECARD 130POS .100 EXTEND |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 24AA01B-E/MC | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:1K I2C⑩ Serial EEPROM |

| 24AA01B-E/MS | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:1K I2C⑩ Serial EEPROM |

| 24AA01B-E/OT | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:1K I2C⑩ Serial EEPROM |

| 24AA01B-E/P | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:1K I2C⑩ Serial EEPROM |

| 24AA01B-E/SN | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:1K I2C⑩ Serial EEPROM |

发布紧急采购,3分钟左右您将得到回复。