- 您现在的位置:买卖IC网 > Datasheet目录286 > 24AA025E48T-I/SN (Microchip Technology)IC EEPROM SER 2K I2C 8-SOIC Datasheet资料下载

参数资料

| 型号: | 24AA025E48T-I/SN |

| 厂商: | Microchip Technology |

| 文件页数: | 11/28页 |

| 文件大小: | 0K |

| 描述: | IC EEPROM SER 2K I2C 8-SOIC |

| 标准包装: | 3,300 |

| 格式 - 存储器: | EEPROMs - 串行 |

| 存储器类型: | EEPROM |

| 存储容量: | 2K (256 x 8) |

| 速度: | 100kHz,400kHz |

| 接口: | I²C,2 线串口 |

| 电源电压: | 1.7 V ~ 5.5 V |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 8-SOIC(0.154",3.90mm 宽) |

| 供应商设备封装: | 8-SOICN |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

�� �

�

�

�24AA02E48/24AA025E48�

�8.0�

�READ� OPERATION�

�8.3�

�Sequential� Read�

�Read� operations� are� initiated� in� the� same� way� as� write�

�operations,� with� the� exception� that� the� R/W� bit� of� the�

�slave� address� is� set� to� ‘� 1� ’.� There� are� three� basic� types�

�of� read� operations:� current� address� read,� random� read�

�and� sequential� read.�

�Sequential� reads� are� initiated� in� the� same� way� as� a�

�random� read,� except� that� once� the� 24AAXXXE48� trans-�

�mits� the� first� data� byte,� the� master� issues� an� acknowl-�

�edge� as� opposed� to� a� Stop� condition� in� a� random� read.�

�This� directs� the� 24AAXXXE48� to� transmit� the� next�

�sequentially-addressed� 8-bit� word� (Figure� 8-3).�

�8.1�

�Current� Address� Read�

�To� provide� sequential� reads,� the� 24AAXXXE48� con-�

�The� 24AAXXXE48� contains� an� address� counter� that�

�maintains� the� address� of� the� last� word� accessed,� inter-�

�nally� incremented� by� ‘� 1� ’.� Therefore,� if� the� previous�

�access� (either� a� read� or� write� operation)� was� to� address�

�tains� an� internal� Address� Pointer� that� is� incremented� by�

�one� upon� completion� of� each� operation.� This� Address�

�Pointer� allows� the� entire� memory� contents� to� be� serially�

�read� during� one� operation.�

�n� ,� the� next� current� address� read� operation� would�

�access� data� from� address� n� +� 1� .� Upon� receipt� of� the�

�8.4�

�Noise� Protection�

�slave� address� with� R/W� bit� set� to� ‘� 1� ’,� the� 24AAXXXE48�

�issues� an� acknowledge� and� transmits� the� 8-bit� data�

�word.� The� master� will� not� acknowledge� the� transfer,� but�

�does� generate� a� Stop� condition,� and� the� 24AAXXXE48�

�discontinues� transmission� (Figure� 8-1).�

�The� 24AAXXXE48� employs� a� V� CC� threshold� detector�

�circuit� which� disables� the� internal� erase/write� logic� if� the�

�V� CC� is� below� 1.5V� at� nominal� conditions.�

�The� SCL� and� SDA� inputs� have� Schmitt� Trigger� and�

�filter� circuits� which� suppress� noise� spikes� to� assure�

�8.2�

�Random� Read�

�proper� device� operation,� even� on� a� noisy� bus.�

�Random� read� operations� allow� the� master� to� access�

�any� memory� location� in� a� random� manner.� To� perform�

�this� type� of� read� operation,� the� word� address� must� first�

�be� set.� This� is� accomplished� by� sending� the� word�

�address� to� the� 24AAXXXE48� as� part� of� a� write� opera-�

�tion.� Once� the� word� address� is� sent,� the� master� gener-�

�ates� a� Start� condition� following� the� acknowledge.� This�

�terminates� the� write� operation,� but� not� before� the� inter-�

�nal� Address� Pointer� is� set.� The� master� then� issues� the�

�control� byte� again,� but� with� the� R/W� bit� set� to� a� ‘� 1� ’.� The�

�24AAXXXE48� will� then� issue� an� acknowledge� and�

�transmit� the� 8-bit� data� word.� The� master� will� not�

�acknowledge� the� transfer,� but� does� generate� a� Stop�

�condition,� and� the� 24AAXXXE48� will� discontinue�

�transmission� (Figure� 8-2).�

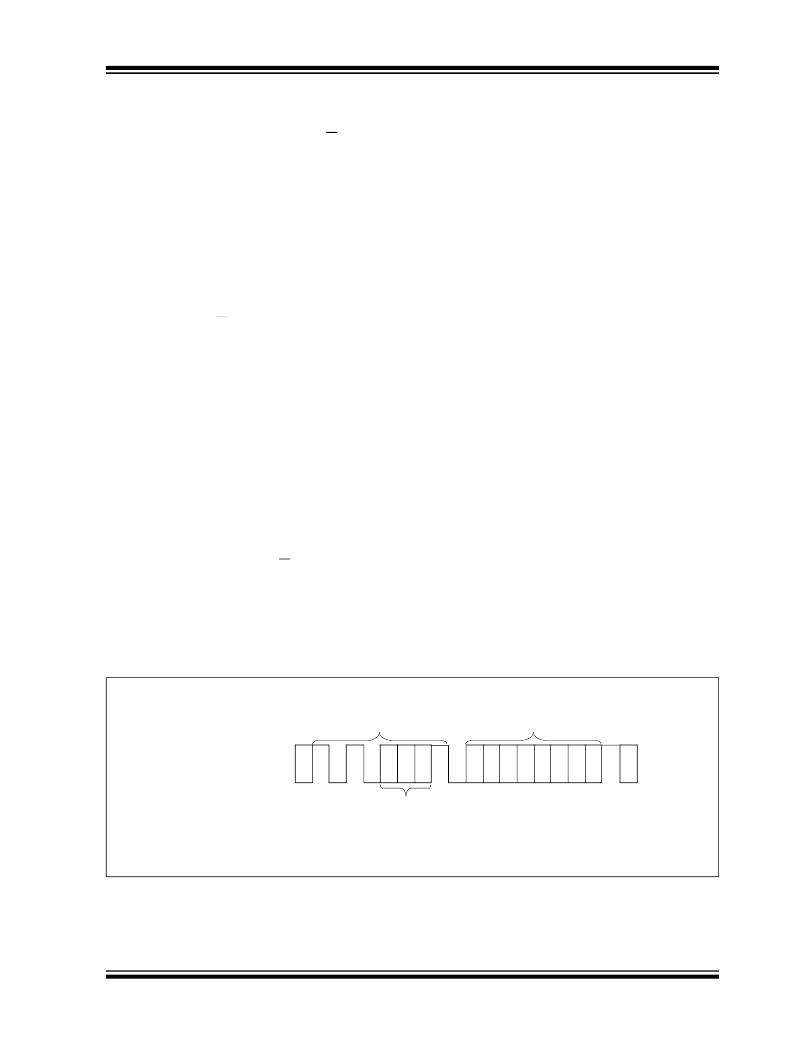

�FIGURE� 8-1:�

�CURRENT� ADDRESS� READ�

�Bus� Activity�

�Master�

�S�

�T�

�A�

�R�

�T�

�Control�

�Byte�

�Data� (n)�

�S�

�T�

�O�

�P�

�SDA� Line�

�Bus� Activity�

�S� 1�

�0�

�1�

�0� A2*� A1*A0*� 1�

�Chip�

�Select�

�Bits�

�A�

�C�

�K�

�N�

�o�

�A�

�C�

�K�

�P�

�Note:�

�*� Bits� A0,� A1� and� A2� are� “don’t� cares”� for� the� 24AA02E48.�

�?� 2010� Microchip� Technology� Inc.�

�DS22124D-page� 11�

�相关PDF资料 |

PDF描述 |

|---|---|

| 24AA02H-I/MS | IC EEPROM 2KBIT 400KHZ 8MSOP |

| 24AA02T/ST | IC EEPROM 2KBIT 400KHZ 8TSSOP |

| 24AA08/ST | IC EEPROM 8KBIT 400KHZ 8TSSOP |

| 24AA16-I/STG | IC EEPROM 16KBIT 400KHZ 8TSSOP |

| 24AA256-I/MS | IC EEPROM 256KBIT 400KHZ 8MSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 24AA025E48-TOT | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:2K I2C? Serial EEPROMs with EUI-48? Node Identity |

| 24AA025E48-TSN | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:2K I2C? Serial EEPROMs with EUI-48? Node Identity |

| 24AA025E48T-TOT | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:2K I2C? Serial EEPROMs with EUI-48? Node Identity |

| 24AA025E48T-TSN | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:2K I2C? Serial EEPROMs with EUI-48? Node Identity |

| 24AA025E64 | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:2K I2Ca?¢ Serial EEPROMs with EUI-48a?¢ or EUI-64a?¢ Node Identity |

发布紧急采购,3分钟左右您将得到回复。