- 您现在的位置:买卖IC网 > PDF目录155699 > 24C04A-EP (Microchip Technology Inc.) 1K/2K/4K 5.0V I 2 C O Serial EEPROMs PDF资料下载

参数资料

| 型号: | 24C04A-EP |

| 厂商: | Microchip Technology Inc. |

| 英文描述: | 1K/2K/4K 5.0V I 2 C O Serial EEPROMs |

| 中文描述: | 1K/2K/4K 5.0VI 2二氧化碳串行EEPROM |

| 文件页数: | 8/12页 |

| 文件大小: | 107K |

| 代理商: | 24C04A-EP |

1998 Microchip Technology Inc.

DS11183E-page 5

24C04A

4.0

SLAVE ADDRESS

The chip address inputs A1 and A2 must be externally

connected to either VCC or ground (VSS), thereby

assigning a unique address to each device. A0 is not

used on the 24C04A and must be connected to either

VCC or VSS. Up to four 24C04A devices may be con-

nected to the bus. Chip selection is then accomplished

through software by setting the bits A1 and A2 of the

slave address to the corresponding hard-wired logic lev-

els of the selected 24C04A. After generating a START

condition, the bus master transmits the slave address

consisting of a 4-bit device code (1010), followed by the

chip address bits A0, A1 and A2. The seventh bit of that

byte (A0) is used to select the upper block (addresses

100—1FF) or the lower block (addresses 000—0FF) of

the array.

The eighth bit of the slave address determines if the

master device wants to read or write to the 24C04A

The 24C04A monitors the bus for its corresponding

slave address all the time. It generates an acknowl-

edge bit if the slave address was true and it is not in a

programming mode.

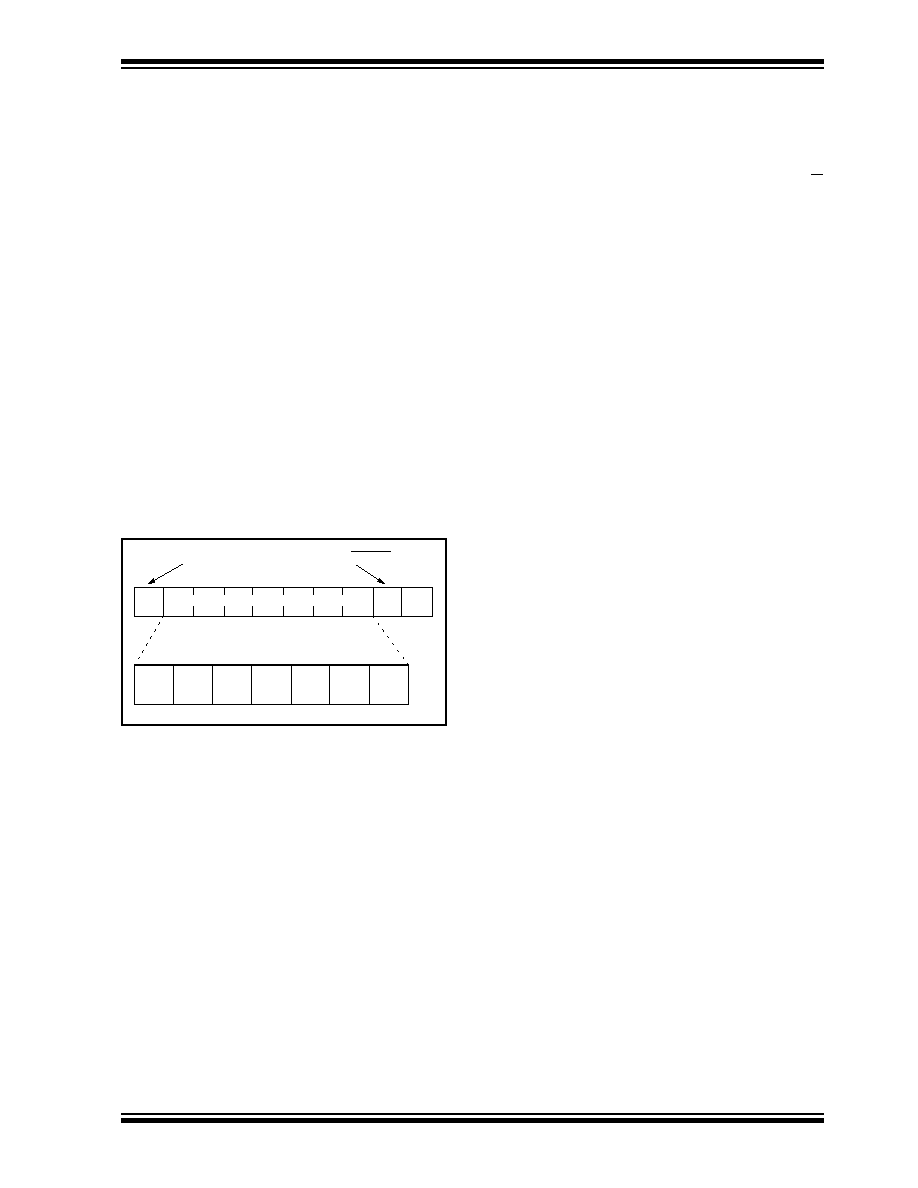

FIGURE 4-1:

SLAVE ADDRESS

ALLOCATION

SLAVE ADDRESS

101

0A2

A1

A0

R/W

A

START

READ/WRITE

5.0

BYTE PROGRAM MODE

In this mode, the master sends addresses and one

data byte to the 24C04A.

Following the START signal from the master, the device

code (4-bits), the slave address (3-bits), and the R/W

bit, which is logic LOW, are placed onto the bus by the

master. This indicates to the addressed 24C04A that a

byte with a word address will follow after it has gener-

ated an acknowledge bit. Therefore the next byte trans-

mitted by the master is the word address and will be

written into the address pointer of the 24C04A. After

receiving the acknowledge, the master device trans-

mits the data word to be written into the addressed

memory location. The 24C04A acknowledges again

and the master generates a STOP condition. This ini-

tiates the internal programming cycle (Figure 6-1).

相关PDF资料 |

PDF描述 |

|---|---|

| 24C04A-ESL | 1K/2K/4K 5.0V I 2 C O Serial EEPROMs |

| 24C04A-ESM | 1K/2K/4K 5.0V I 2 C O Serial EEPROMs |

| 24C04A-ESN | 1K/2K/4K 5.0V I 2 C O Serial EEPROMs |

| 24C04A-IP | 1K/2K/4K 5.0V I 2 C O Serial EEPROMs |

| 24C04A-ISL | 1K/2K/4K 5.0V I 2 C O Serial EEPROMs |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 24C04A-ESL | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:4K 5.0V I 2 C ⑩ Serial EEPROM |

| 24C04A-ESM | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:4K 5.0V I 2 C ⑩ Serial EEPROM |

| 24C04A-ESN | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:4K 5.0V I 2 C ⑩ Serial EEPROM |

| 24C04A-I/J | 制造商:未知厂家 制造商全称:未知厂家 功能描述:I2C Serial EEPROM |

| 24C04A-I/P | 制造商:未知厂家 制造商全称:未知厂家 功能描述:I2C Serial EEPROM |

发布紧急采购,3分钟左右您将得到回复。