参数资料

| 型号: | 25LC040-I/SN |

| 厂商: | Microchip Technology |

| 文件页数: | 10/22页 |

| 文件大小: | 0K |

| 描述: | IC EEPROM 4KBIT 2MHZ 8SOIC |

| 标准包装: | 100 |

| 格式 - 存储器: | EEPROMs - 串行 |

| 存储器类型: | EEPROM |

| 存储容量: | 4K (512 x 8) |

| 速度: | 2MHz |

| 接口: | SPI 3 线串行 |

| 电源电压: | 2.5 V ~ 5.5 V |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 8-SOIC(0.154",3.90mm 宽) |

| 供应商设备封装: | 8-SOICN |

| 包装: | 管件 |

| 产品目录页面: | 1448 (CN2011-ZH PDF) |

�� �

�

�

�25AA040/25LC040/25C040�

�3.5�

�Read� Status� Register� (RDSR)�

�3.6�

�Write� Status� Register� (WRSR)�

�The� RDSR� instruction� provides� access� to� the� STATUS�

�register.� The� STATUS� register� may� be� read� at� any� time,�

�even� during� a� write� cycle.� The� STATUS� register� is�

�formatted� as� follows:�

�The� WRSR� instruction� allows� the� user� to� select� one� of�

�four� levels� of� protection� for� the� array� by� writing� to� the�

�appropriate� bits� in� the� STATUS� register.� The� array� is�

�divided� up� into� four� segments.� The� user� has� the� ability�

�7�

�X�

�6�

�X�

�5�

�X�

�4�

�X�

�3�

�BP1�

�2�

�BP0�

�1�

�WEL�

�0�

�WIP�

�to� write-protect� none,� one,� two,� or� all� four� of� the�

�segments� of� the� array.� The� partitioning� is� controlled� as�

�illustrated� in� Table� 3-2.�

�The� Write-In-Process� (WIP)� bit� indicates� whether� the�

�25XX040� is� busy� with� a� write� operation.� When� set� to� a�

�See� Figure� 3-7� for� WRSR� timing� sequence.�

�‘� 1� ’,� a� write� is� in� progress,� when� set� to� a� ‘� 0� ’,� no� write� is�

�in� progress.� This� bit� is� read-only.�

�TABLE� 3-2:�

�ARRAY� PROTECTION�

�The� Write� Enable� Latch� (WEL)� bit� indicates� the� status�

�of� the� write� enable� latch.� When� set� to� a� ‘� 1� ’,� the� latch�

�allows� writes� to� the� array,� when� set� to� a� ‘� 0� ’,� the� latch�

�prohibits� writes� to� the� array.� The� state� of� this� bit� can�

�always� be� updated� via� the� WREN� or� WRDI� commands�

�regardless� of� the� state� of� write� protection� on� the�

�STATUS� register.� This� bit� is� read-only.�

�The� Block� Protection� (BP0� and� BP1)� bits� indicate�

�which� blocks� are� currently� write-protected.� These� bits�

�are� set� by� the� user� issuing� the� WRSR� instruction.� These�

�BP1�

�0�

�0�

�1�

�1�

�BP0�

�0�

�1�

�0�

�1�

�Array� Addresses�

�Write-Protected�

�none�

�upper� 1/4�

�(0180h-01FFh)�

�upper� 1/2�

�(0100h-01FFh)�

�all�

�(0000h-01FFh)�

�bits� are� nonvolatile.�

�See� Figure� 3-6� for� RDSR� timing� sequence.�

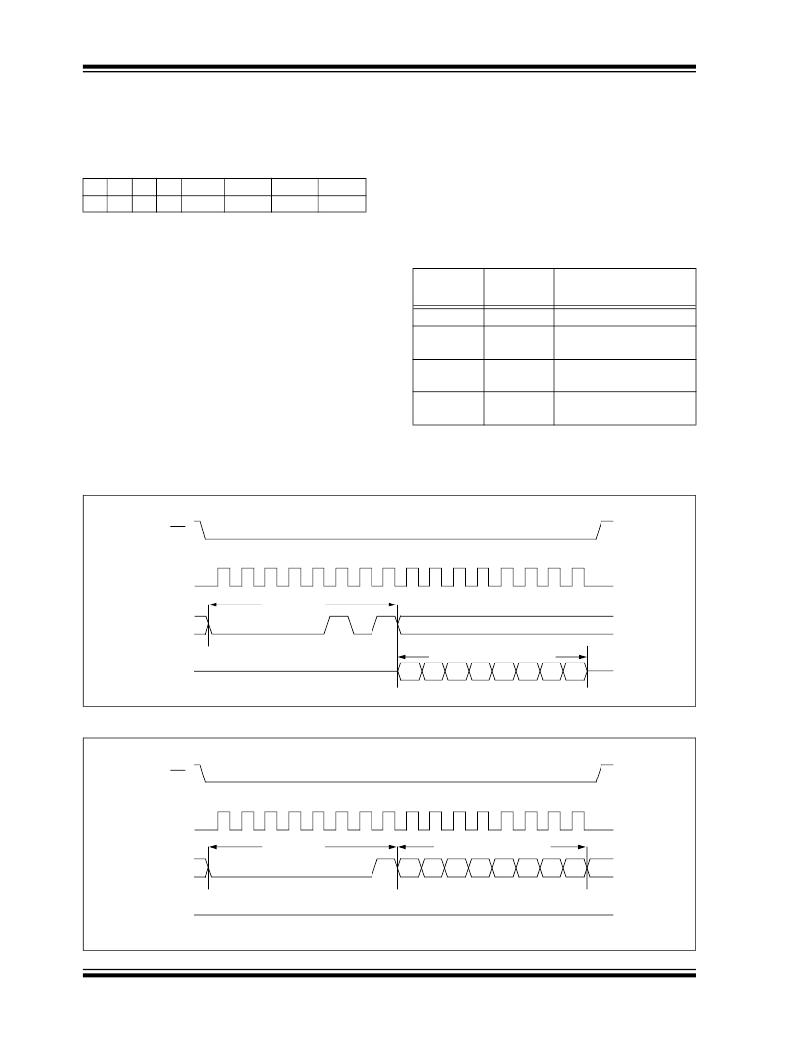

�FIGURE� 3-6:�

�CS�

�READ� STATUS� REGISTER� SEQUENCE�

�0�

�1�

�2�

�3�

�4�

�5�

�6�

�7�

�8�

�9�

�10�

�11�

�12�

�13�

�14�

�15�

�SCK�

�Instruction�

�SI�

�0�

�0�

�0�

�0�

�0�

�1�

�0�

�1�

�SO�

�High-impedance�

�7�

�Data� from� STATUS� register�

�6� 5� 4� 3� 2� 1�

�0�

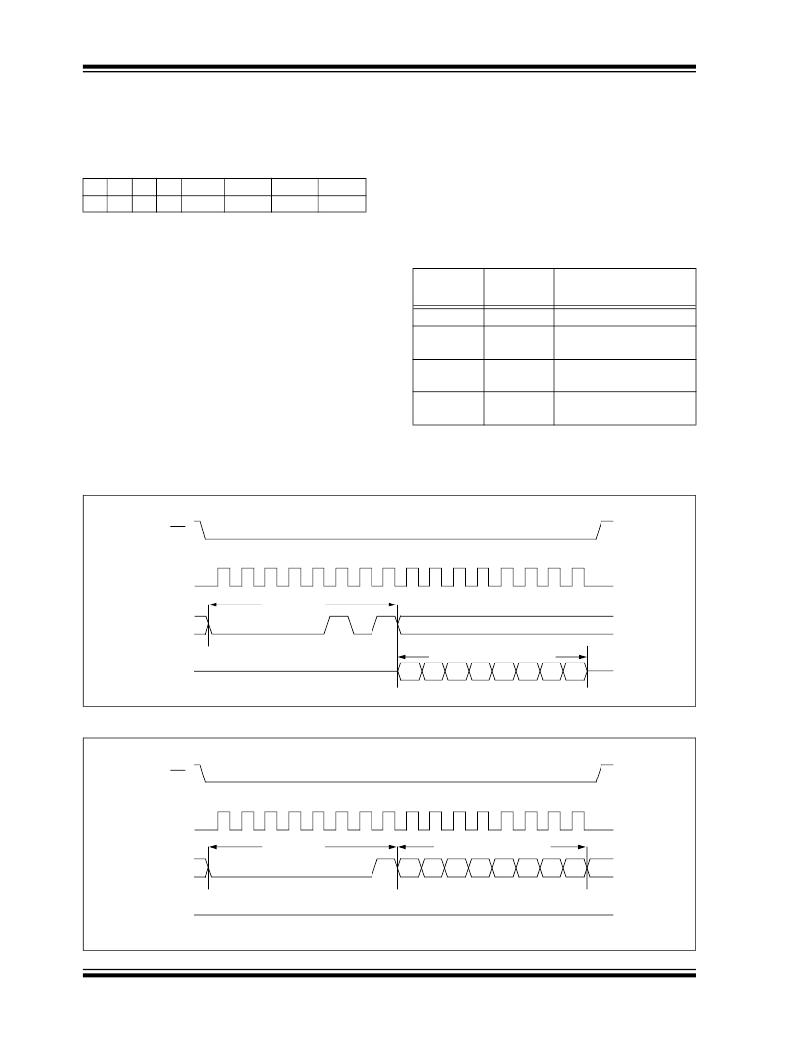

�FIGURE� 3-7:�

�CS�

�WRITE� STATUS� REGISTER� SEQUENCE�

�0�

�1�

�2�

�3�

�4�

�5�

�6�

�7�

�8�

�9�

�10�

�11�

�12�

�13�

�14�

�15�

�SCK�

�Instruction�

�Data� to� STATUS� register�

�SI�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�1�

�7�

�6�

�5�

�4�

�3�

�2�

�1�

�0�

�High-impedance�

�SO�

�DS21204E-page� 10�

�?� 2006� Microchip� Technology� Inc.�

�相关PDF资料 |

PDF描述 |

|---|---|

| 25AA040-I/SN | IC EEPROM 4KBIT 1MHZ 8SOIC |

| 25LC040/SN | IC EEPROM 4KBIT 2MHZ 8SOIC |

| GMM44DRAN | CONN EDGECARD 88POS R/A .156 SLD |

| GSM44DRAH | CONN EDGECARD 88POS R/A .156 SLD |

| GMM44DRAH | CONN EDGECARD 88POS R/A .156 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 25LC040N | 制造商:未知厂家 制造商全称:未知厂家 功能描述:EEPROM |

| 25LC040P | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:4K SPI Bus Serial EEPROM |

| 25LC040-P | 制造商:未知厂家 制造商全称:未知厂家 功能描述:SPI Serial EEPROM |

| 25LC040-SN | 制造商:未知厂家 制造商全称:未知厂家 功能描述:SPI Serial EEPROM |

| 25LC040ST | 制造商:未知厂家 制造商全称:未知厂家 功能描述:EEPROM |

发布紧急采购,3分钟左右您将得到回复。