- 您现在的位置:买卖IC网 > PDF目录156551 > 37C67X (SMSC Corporation) ENHANCED SUPER I/O CONTROLLER WITH FAST IR PDF资料下载

参数资料

| 型号: | 37C67X |

| 厂商: | SMSC Corporation |

| 英文描述: | ENHANCED SUPER I/O CONTROLLER WITH FAST IR |

| 中文描述: | 增强的超级I / O控制器,快速红外线 |

| 文件页数: | 171/194页 |

| 文件大小: | 546K |

| 代理商: | 37C67X |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页当前第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页第190页第191页第192页第193页第194页

78

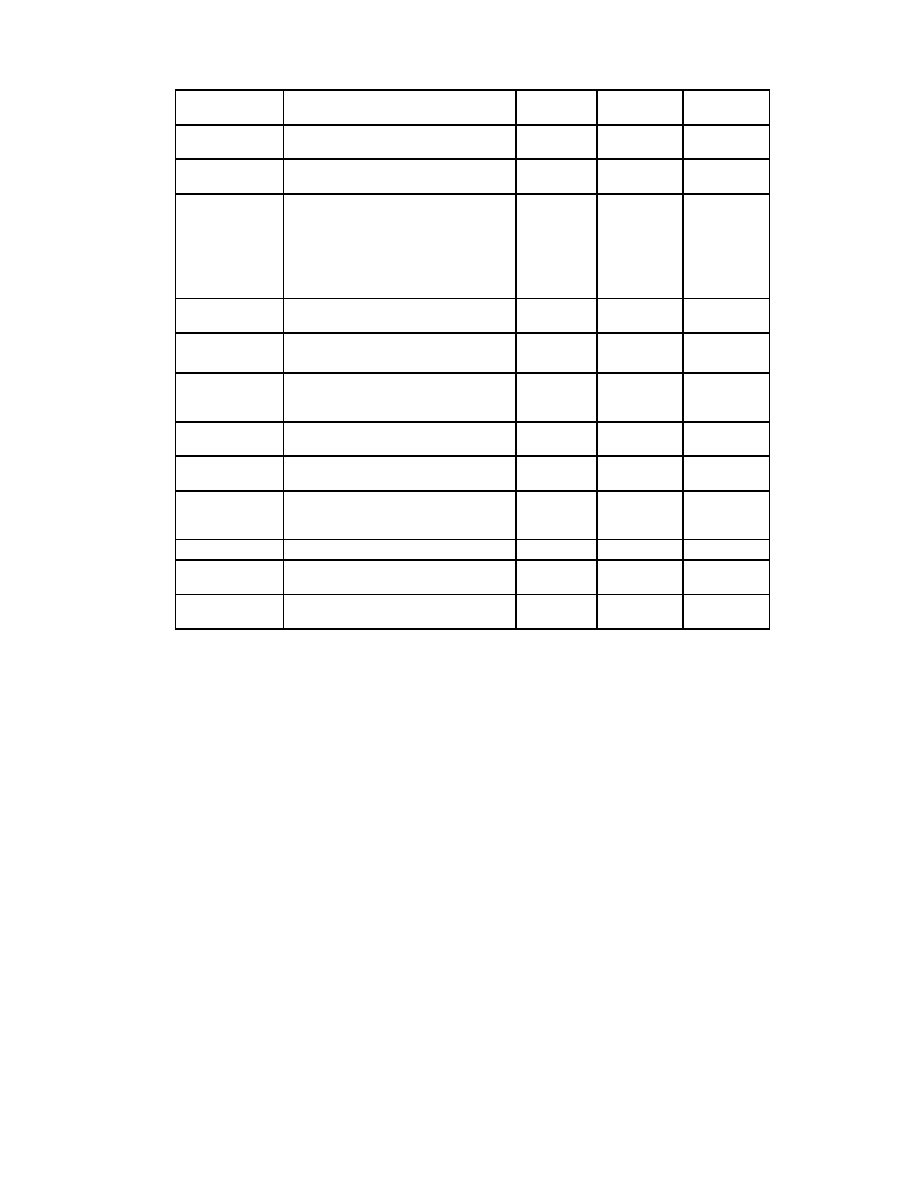

Table 35 - Register Summary for an Individual UART Channel

REGISTER

ADDRESS*

REGISTER NAME

REGISTER

SYMBOL

BIT 0

BIT 1

ADDR = 0

DLAB = 0

Receive Buffer Register (Read Only)

RBR

Data Bit 0

(Note 1)

Data Bit 1

ADDR = 0

DLAB = 0

Transmitter Holding Register (Write Only)

THR

Data Bit 0

Data Bit 1

ADDR = 1

DLAB = 0

Interrupt Enable Register

IER

Enable

Received Data

Available

Interrupt

(ERDAI)

Enable

Transmitter

Holding

Register

Empty

Interrupt

(ETHREI)

ADDR = 2

Interrupt Ident. Register (Read Only)

IIR

"0" if Interrupt

Pending

Interrupt ID Bit

ADDR = 2

FIFO Control Register (Write Only)

FCR

(Note 7)

FIFO Enable

RCVR FIFO

Reset

ADDR = 3

Line Control Register

LCR

Word Length

Select Bit 0

(WLS0)

Word Length

Select Bit 1

(WLS1)

ADDR = 4

MODEM Control Register

MCR

Data Terminal

Ready (DTR)

Request to

Send (RTS)

ADDR = 5

Line Status Register

LSR

Data Ready

(DR)

Overrun Error

(OE)

ADDR = 6

MODEM Status Register

MSR

Delta Clear to

Send (DCTS)

Delta Data Set

Ready

(DDSR)

ADDR = 7

Scratch Register (Note 4)

SCR

Bit 0

Bit 1

ADDR = 0

DLAB = 1

Divisor Latch (LS)

DDL

Bit 0

Bit 1

ADDR = 1

DLAB = 1

Divisor Latch (MS)

DLM

Bit 8

Bit 9

*DLAB is Bit 7 of the Line Control Register (ADDR = 3).

Note 1: Bit 0 is the least significant bit. It is the first bit serially transmitted or received.

Note 2: When operating in the XT mode, this bit will be set any time that the transmitter shift

register is empty.

相关PDF资料 |

PDF描述 |

|---|---|

| 37C957FR | ULTRA I/O CONTROLLER FOR PORTABLE APPLICATIONS |

| 37FMA1-ABW31N | SPECIAL SWITCH-PIEZO SWITCH, SPST, MOMENTARY, 0.2A, 24VDC, PANEL MOUNT-THREADED |

| 37FML1-BEW31N | SPECIAL SWITCH-PIEZO SWITCH, SPST, MOMENTARY, 0.2A, 24VDC, PANEL MOUNT-THREADED |

| 37FML2-ACW21N | SPECIAL SWITCH-PIEZO SWITCH, SPST, MOMENTARY, 1A, 24VDC, PANEL MOUNT-THREADED |

| 37FMA1-AAW11N | SPECIAL SWITCH-PIEZO SWITCH, SPST, MOMENTARY, 0.2A, 24VDC, PANEL MOUNT-THREADED |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 37C-6BH-5-5 | 制造商:Birtcher Products 功能描述: |

| 37C72U-185 | 制造商:White-Rodgers 功能描述: |

| 37C73U-170 | 制造商:White-Rodgers 功能描述: |

| 37C73U-171 | 制造商:White-Rodgers 功能描述: |

| 37C922BQFP | 制造商:SMSC 功能描述: |

发布紧急采购,3分钟左右您将得到回复。