- 您现在的位置:买卖IC网 > PDF目录67337 > 5962-9457501Q2A (TEXAS INSTRUMENTS INC) 0.5 A SWITCHING CONTROLLER, 1000 kHz SWITCHING FREQ-MAX, CQCC20 PDF资料下载

参数资料

| 型号: | 5962-9457501Q2A |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 稳压器 |

| 英文描述: | 0.5 A SWITCHING CONTROLLER, 1000 kHz SWITCHING FREQ-MAX, CQCC20 |

| 封装: | CERAMIC, LCC-20 |

| 文件页数: | 27/31页 |

| 文件大小: | 1044K |

| 代理商: | 5962-9457501Q2A |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页当前第27页第28页第29页第30页第31页

UCC1806

UCC2806

UCC3806

SLUS272F -- FEBRUARY 2000 -- REVISED AUGUST 2006

5

www.ti.com

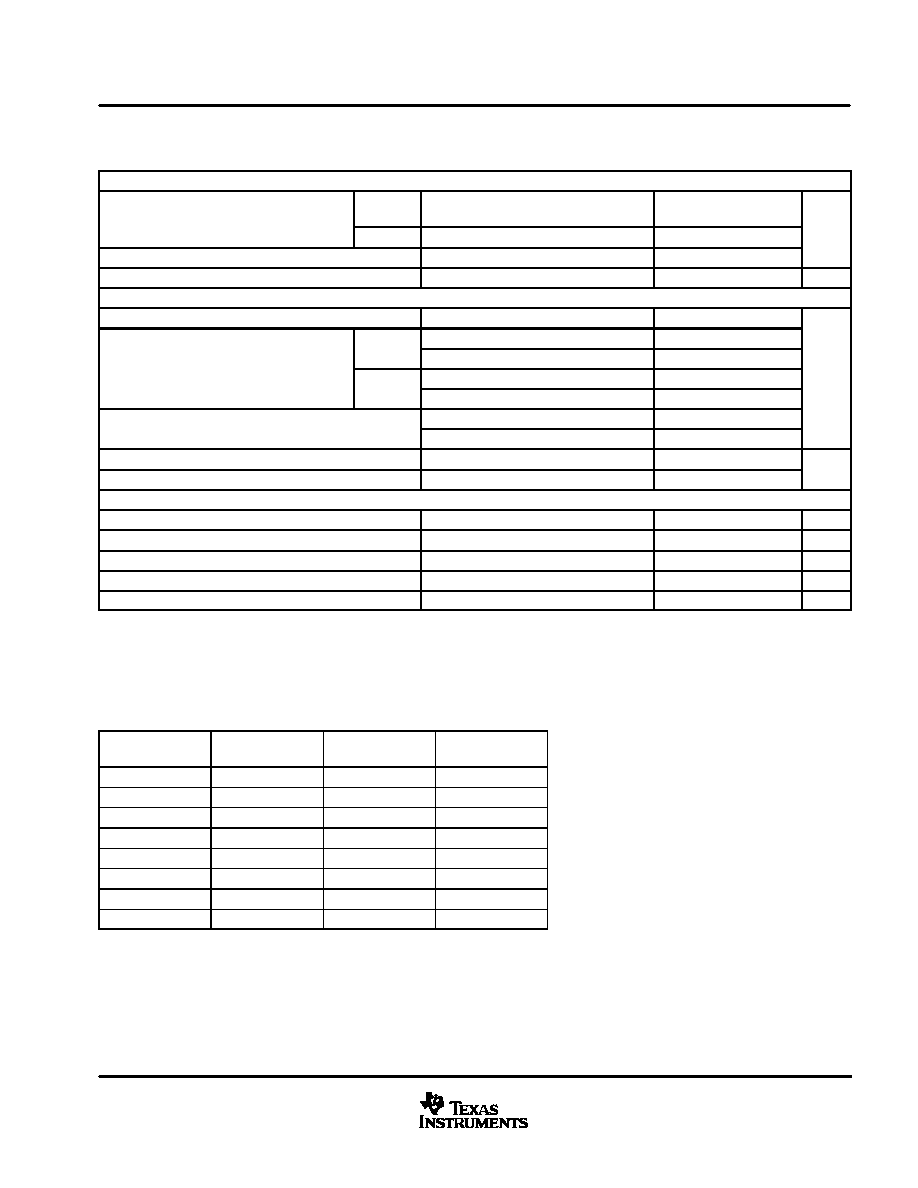

ELECTRICAL CHARACTERISTICS

VIN =12V,RT =33k,CT = 330 pF, CBYPASS on VREF =0.01 μF, --55°C to 125°C for the UCC1806, --40°C<TA <85°C for the UCC2806,

0°C<TA <70°C for the UCC3806, and TA =TJ (unless otherwise noted)

SHUTDOWN TERMINAL

Threshold voltage

UCC1806

UCC2806

0.94

1.00

1.06

V

Threshold voltage

UCC3806

0.9

1.0

1.1

V

Input voltage range

0

VIN

tDLY

Delay-to-output time

0V ≤ VSHUTDOWN ≤ 1.3 V

75

150

ns

OUTPUT

Output supply voltage

2.5

15.0

UCC1806

ISINK =20mA

100

300

Low level output voltage

UCC1806

UCC2806

ISINK = 100 mA

0.4

1.1

Low-level output voltage

UCC3806

ISINK =20mA

100

200

V

UCC3806

ISINK = 100 mA

0.4

1.1

V

High level output voltage

ISRC =--20 mA

11.6

11.9

High-level output voltage

ISRC = --100 mA

11.0

11.6

tRISE

Rise time

TJ =25°C,

CLOAD = 1000 pF

35

65

ns

tFALL

Fall time

TJ =25°C,

CLOAD = 1000 pF

35

65

ns

UNDERVOLTAGE LOCKOUT (UVLO)

VSTART Startup threshold voltage

6.5

7.5

8.0

V

Threshold hysteresis

0.75

V

ISTART

Startup current

VIN <VSTART

50

100

μA

I

Operating supply current

1.0

1.4

mA

VIN shunt voltage

IVIN =10mA

15.0

17.5

(1)

Line range = 10 V to 15 V, load range = 0.2 mA to 5 mA

(2)

Ensured by design. Not production tested.

(3)

Parameters measured at trip point of latch with VNI =VREF,VINV =0V.

(4)

Amplifier gain defined as: G = delta change at COMP /delta change forced at CS+ delta voltage at CS+ = 0 to 1V

(5)

Current-sense amplifier output is slew rate limited to provide noise immunity.

THERMAL RESISTANCE TABLE

PACKAGE

DESIGNATOR

PACKAGE TYPE

θJC

(°C/W)

θJA

(°C/W)

D

SOIC--16

35

50 to 120(1)

DW

SOICW--16

27

50 to 100(1)

J

CDIP--16

28

80 to 120

L

CLCC--20

20

70 to 80

M

SSOP--16

38

144 to 172(2)

N

PDIP--16

45

90(1)

PW

TSSOP--16

15

123 to 147(2)

Q

PLCC--20

34

43 to 75(1)

(1) Specified θ JA (junction to ambient) is for devices mounted to 5 in2 FR4 PC board

with one ounce copper where noted. When resistance range is given, lower values

are for 5 in2 aluminum PC board. Test PWB was 0.062 in thick and typically used

0.635 mm trace widths for power packages and 1.3 mm trace widths for non-power

packages with a 100x100 mil probe land area at the end of each trace.

(2) Modeled data. If value range given for θ JA, the lower value is for 3x3 inch1 oz

internal copper ground plane, and the higher value is for 1x1 inch ground plane. All

model data assumes only one trace for each non-fused lead.

相关PDF资料 |

PDF描述 |

|---|---|

| 5962-9457501QEA | 1 A SWITCHING CONTROLLER, 1000 kHz SWITCHING FREQ-MAX, CDIP16 |

| 5962-9457501V2A | 0.5 A SWITCHING CONTROLLER, 1000 kHz SWITCHING FREQ-MAX, CQCC20 |

| 5962-9457501VEA | 0.5 A SWITCHING CONTROLLER, 1000 kHz SWITCHING FREQ-MAX, CDIP16 |

| 5962-9462101MPX | SWITCHING REGULATOR, CDIP8 |

| 5962-9462201Q2A | FLUORESCENT LIGHT CONTROLLER, 78 kHz SWITCHING FREQ-MAX, CQCC20 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 5962-9457501QEA | 制造商:Texas Instruments 功能描述:UCC1806J883B - Rail/Tube |

| 59629457701QKA | 制造商:Texas Instruments 功能描述:54ABT646W |

| 5962-9457701QLA | 制造商:QP Semiconductor 功能描述:BUS XCVR SINGLE 8-CH 3-ST 24-PIN CDIP RAIL 制造商:QP Semiconductor 功能描述:Bus XCVR Single 8-CH 3-ST 24-Pin CDIP |

| 5962-9457702Q3A | 制造商:Texas Instruments 功能描述:Bus XCVR Single 8-CH 3-ST 28-Pin LCCC Tube 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| 5962-9457702QKA | 制造商:Texas Instruments 功能描述:Bus XCVR Single 8-CH 3-ST 24-Pin CFPAK Tube |

发布紧急采购,3分钟左右您将得到回复。