- 您现在的位置:买卖IC网 > PDF目录67348 > 5962F1023303VXC 16-CHANNEL, SGL ENDED MULTIPLEXER, CDFP28 PDF资料下载

参数资料

| 型号: | 5962F1023303VXC |

| 元件分类: | 多路复用及模拟开关 |

| 英文描述: | 16-CHANNEL, SGL ENDED MULTIPLEXER, CDFP28 |

| 封装: | CERAMIC, DFP-28 |

| 文件页数: | 7/23页 |

| 文件大小: | 474K |

| 代理商: | 5962F1023303VXC |

15

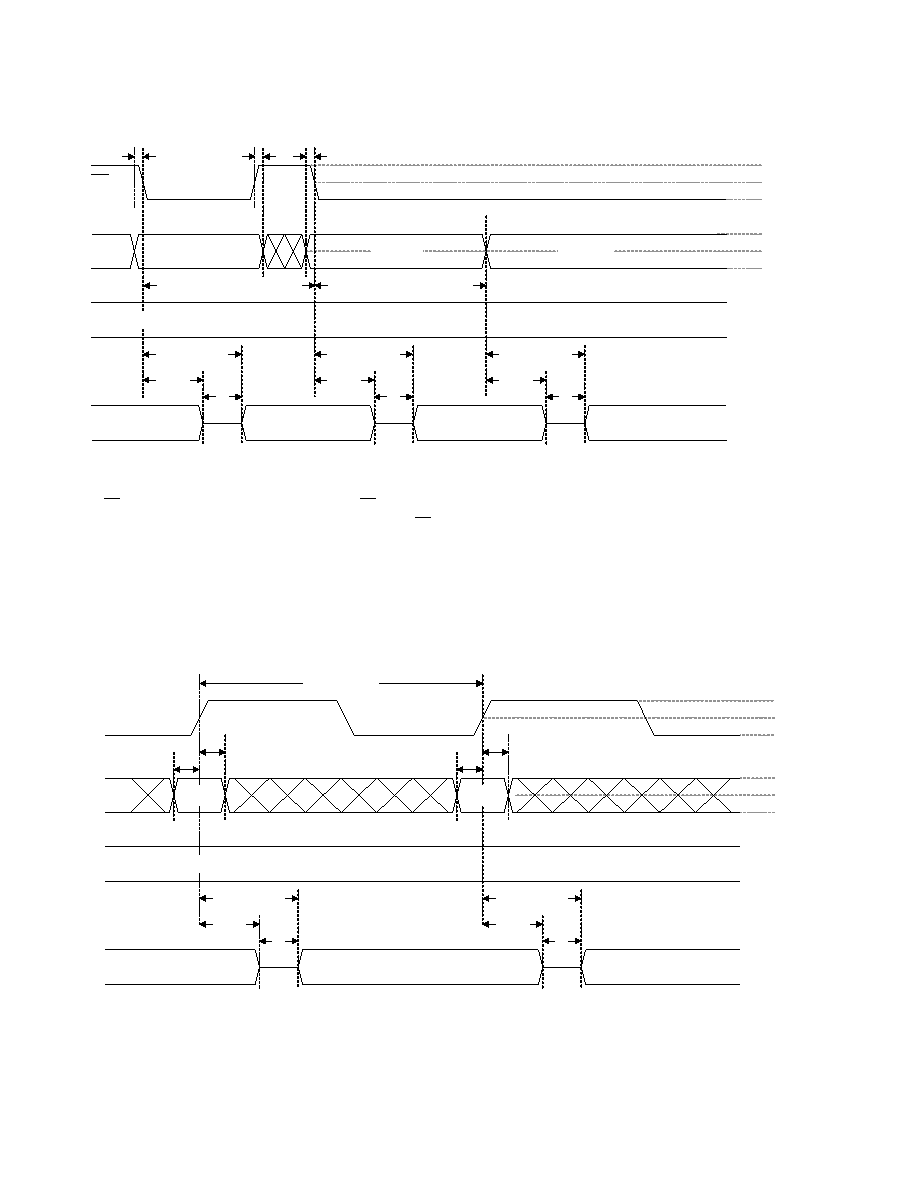

Timing Diagrams

Multiplexer Asynchronous Parallel Timing (UT16MX110)

Multiplexer Synchronous Parallel Timing (UT16MX111)

Am Valid

CS

A[3:0]

S[x] = Analog Inputs

COM

(Previous)

COM = S[Am Valid]

COM = S[An Valid]

tAS1

VDD_IO

50%

GND

VDD_IO

50%

GND

tAS2

ApValid

COM = S[Ap Valid]

tAS1

HiZ

tMUX

tBBM

HiZ

tCYCLE

tPROP_D

AnValid

Note:

1. CS may be held in a continuous low state, holding CS high provides protection for false address change.

2. tCYCLE is the minimum cycle time between the falling edges of CS and/or any address changes. If tCYCLE is shorter than tPROP_D, an

addressing error may occur.

3. All bits (A[3:0]) of any address change should be received by the UT16MX110 within 18ns of the first bit change for proper operation.

tMUX

tBBM

tPROP_D

tMUX

tBBM

tPROP_D

Figure 5. UT16MX110 Timing Diagram

Figure 6. UT16MX111 Timing Diagram

Am Valid

PLATCH

A[3:0]

S[x] = Analog Inputs

COM(Previous)

COM = S[Am Valid]

COM = S[An Valid]

Note:

1. When PLATCH is in a high or low state, it provides protection for false address change.

2. tCYCLE must not be less than the maximum value of tPROP_D.

tLSU

VDD_IO

50%

GND

VDD_IO

50%

GND

tLHD

An Valid

tLSU

tLHD

tCYCLE

HiZ

tMUX

tBBM

tPROP_D

HiZ

tMUX

tBBM

tPROP_D

相关PDF资料 |

PDF描述 |

|---|---|

| 5962R1023304QXC | 16-CHANNEL, SGL ENDED MULTIPLEXER, CDFP28 |

| 5962R1023306VXC | 16-CHANNEL, SGL ENDED MULTIPLEXER, CDFP28 |

| 5962F1023302VXC | 16-CHANNEL, SGL ENDED MULTIPLEXER, CDFP28 |

| 5962F1023301QXC | 16-CHANNEL, SGL ENDED MULTIPLEXER, CDFP28 |

| 5962F1023302QXC | 16-CHANNEL, SGL ENDED MULTIPLEXER, CDFP28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 5962F1023501KXA | 制造商:International Rectifier 功能描述:RAD HARD ULDO - Bulk |

| 5962F1023502K4A | 制造商:International Rectifier 功能描述:RAD HARD ULDO - Bulk |

| 5962F1023502K5A | 制造商:International Rectifier 功能描述:RAD HARD ULDO - Bulk |

| 5962F1023502K6A | 制造商:International Rectifier 功能描述:RAD HARD ULDO - Bulk |

| 5962F1023502KYA | 制造商:International Rectifier 功能描述:RAD HARD ULDO - Bulk |

发布紧急采购,3分钟左右您将得到回复。