- 您现在的位置:买卖IC网 > PDF目录293971 > 5962F9654403QXA OTHER DECODER/DRIVER, CDFP16 PDF资料下载

参数资料

| 型号: | 5962F9654403QXA |

| 元件分类: | 编、解码器及复用、解复用 |

| 英文描述: | OTHER DECODER/DRIVER, CDFP16 |

| 封装: | BOTTOM-BRAZED, CERAMIC, DFP-16 |

| 文件页数: | 6/9页 |

| 文件大小: | 162K |

| 代理商: | 5962F9654403QXA |

6

Notes:

* For devices procured with a total ionizing dose tolerance guarantee, the post-irradiation performance is guaranteed at 25×C per MIL-STD-883 Method 1019, Condition

A up to the maximum TID level procured.

1. Functional tests are conducted in accordance with MIL-STD-883 with the following input test conditions: VIH = VIH(min) + 20%, - 0%; VIL = VIL(max) + 0%, -

50%, as specified herein, for TTL, CMOS, or Schmitt compatible inputs. Devices may be tested using any input voltage within the above specified range, but are

guaranteed to VIH(min) and VIL(max).

2. Supplied as a design limit but not guaranteed or tested.

3. Per MIL-PRF-38535, for current density

≤5.0E5 amps/cm2, the maximum product of load capacitance (per output buffer) times frequency should not exceed 3,765pF/

MHz.

4. Not more than one output may be shorted at a time for maximum duration of one second.

5. Capacitance measured for initial qualification and when design changes may affect the value. Capacitance is measured between the designated terminal and VSS at

frequency of 1MHz and a signal amplitude of 50mV rms maximum.

6. Maximum allowable relative shift equals 50mV.

7. Power dissipation specified per switching output.

8. Parameter guaranteed by design and characterization, but is not tested.

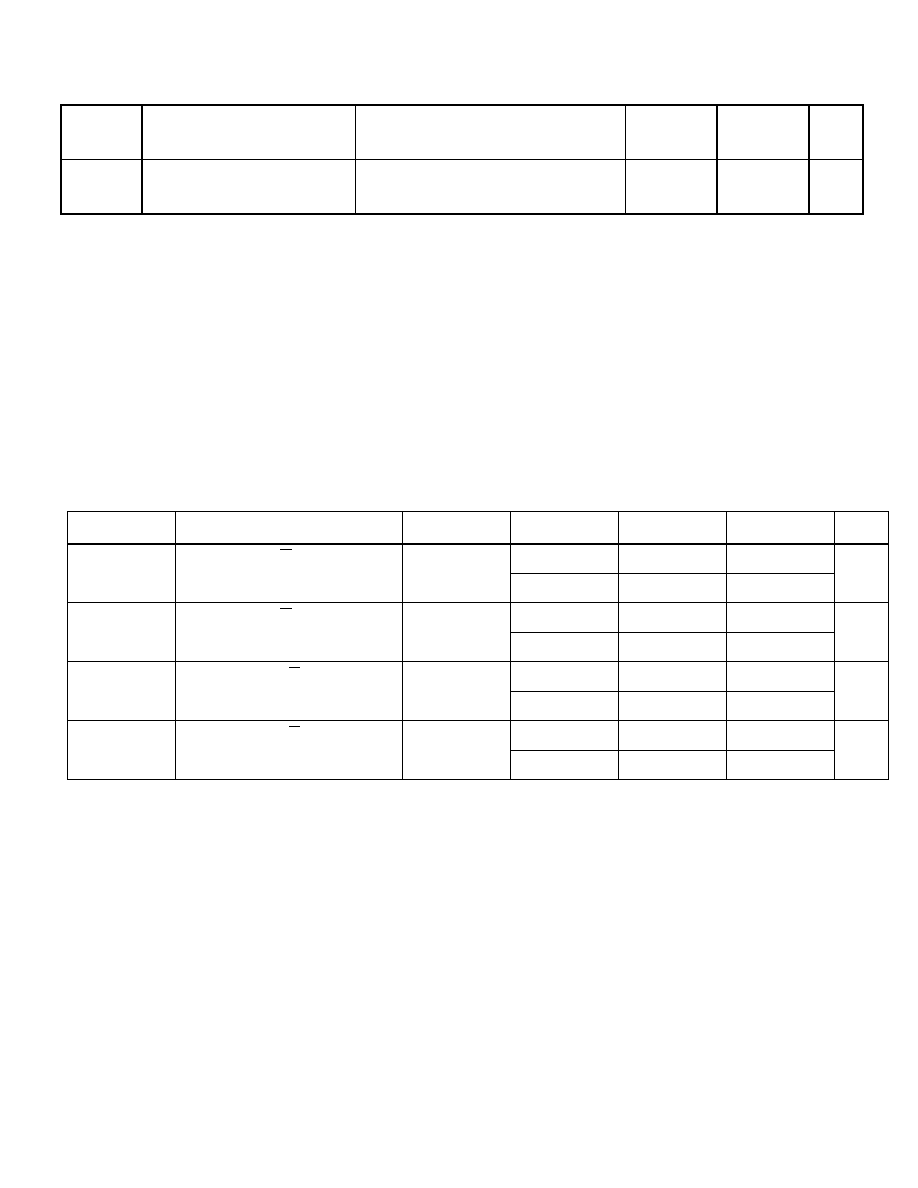

AC ELECTRICAL CHARACTERISTICS (Pre and Post-Radiation)*

(VDD = 3.0V to 5.5V; VSS = 0V

1, -55

°C < T

C < +125°C); Unless otherwise noted, Tc is per the temperature range ordered

Notes:

* For devices procured with a total ionizing dose tolerance guarantee, the post-irradiation performance is guaranteed at 25×C per MIL-STD-883 Method 1019, Condition

A up to the maximum TID level procured.

1. Maximum allowable relative shift equals 50mV.

CIN

Input capacitance 5

= 1MHz

VDD = 0V

15

pF

COUT

Output capacitance 5

= 1MHz

VDD = 0V

15

pF

SYMBOL

PARAMETER

CONDITION

VDD

MINIMUM

MAXIMUM

UNIT

tPLH1

Binary select to Yn

CL = 50pF

3.0V to 3.6V

4

19

ns

4.5V to 5.5V

3

10

tPHL1

Binary select to Yn

CL = 50pF

3.0V to 3.6V

4

19

ns

4.5V to 5.5V

3

10

tPLH2

Enable to Output Yn

CL = 50pF

3.0V to 3.6V

3

19

ns

4.5V to 5.5V

3

10

tPHL2

Enable to Output Yn

CL = 50pF

3.0V to 3.6V

4

19

ns

4.5V to 5.5V

3

10

相关PDF资料 |

PDF描述 |

|---|---|

| 5962F9657601QCX | AC SERIES, 4-BIT LOOK-AHEAD CARRY GENERATOR, TRUE OUTPUT, CDIP16 |

| 5962F9657701VXC | ACT SERIES, 4-BIT LOOK-AHEAD CARRY GENERATOR, TRUE OUTPUT, CDFP16 |

| 5962F9658201QXX | AC SERIES, 9-BIT PARITY GENERATOR/CHECKER, COMPLEMENTARY OUTPUT, CDFP14 |

| 5962G0151601VXA | 8K X 8 OTPROM, 55 ns, CDIP28 |

| 5962H0151601QXC | 8K X 8 OTPROM, 55 ns, CDIP28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 5962F9666301QXC | 制造商:Intersil Corporation 功能描述: |

| 5962F9666302QXC | 制造商:Intersil Corporation 功能描述: |

| 5962F9666302VXC | 制造商:Intersil Corporation 功能描述: |

| 5962F9669601VYC | 制造商:Harris Corporation 功能描述: |

| 5962F9671802VXC | 制造商:INTRSL 功能描述: |

发布紧急采购,3分钟左右您将得到回复。