- 您现在的位置:买卖IC网 > PDF目录293971 > 5962R9581901QQX (INTERSIL CORP) 24 I/O, PIA-GENERAL PURPOSE, CDIP40 PDF资料下载

参数资料

| 型号: | 5962R9581901QQX |

| 厂商: | INTERSIL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 24 I/O, PIA-GENERAL PURPOSE, CDIP40 |

| 封装: | SIDE BRAZED, CERAMIC, DIP-40 |

| 文件页数: | 6/17页 |

| 文件大小: | 232K |

| 代理商: | 5962R9581901QQX |

14

Operating Modes

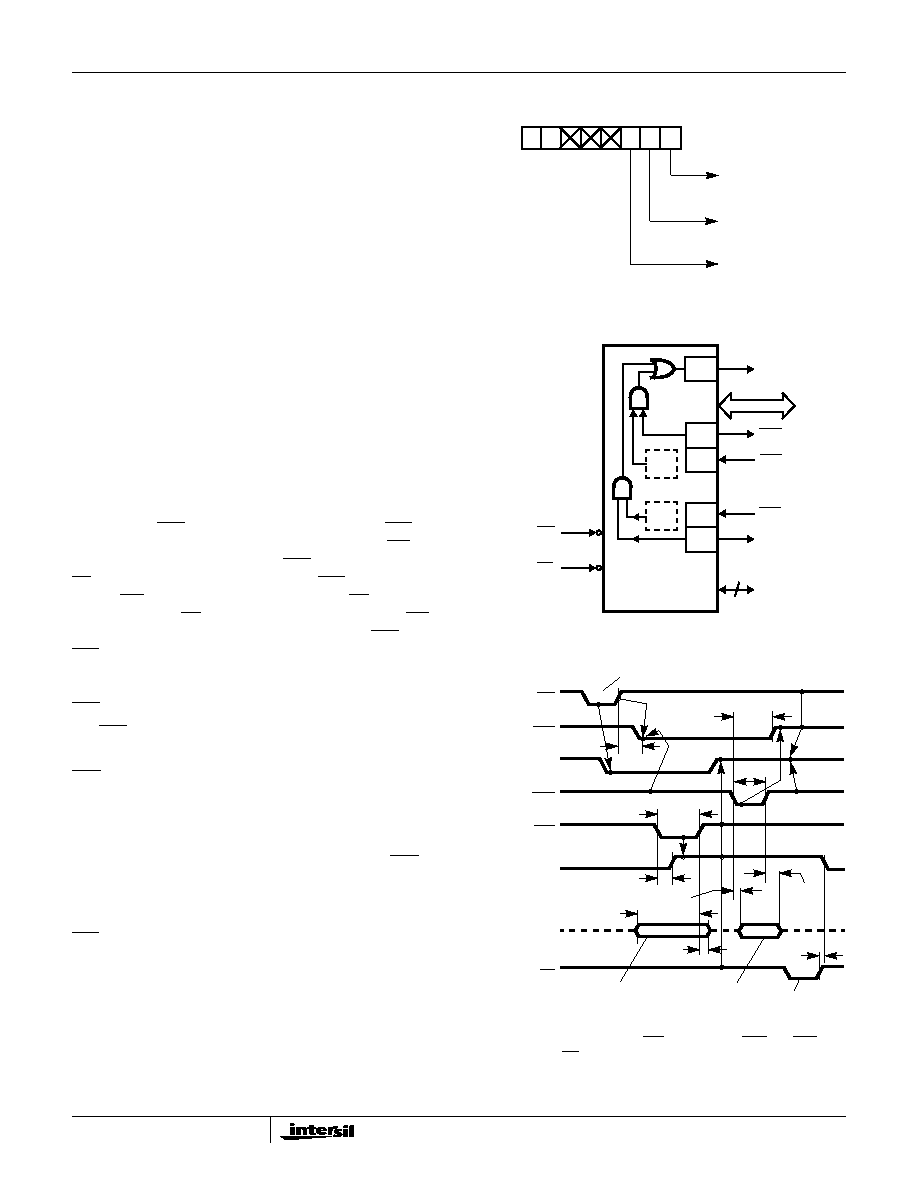

MODE 2 (Strobed Bidirectional Bus I/O)

The functional conguration provides a means for

communicating with a peripheral device or structure on a

single 8-bit bus for both transmitting and receiving data

(bidirectional bus I/O). “Handshaking” signals are provided

to maintain proper bus ow discipline similar to MODE 1.

Interrupt generation and enable/disable functions are also

available.

Mode 2 Basic Functional Denitions:

Used in Group A only.

One 8-bit, bidirectional bus port (Port A) and a 5-bit

control port (Port C).

Both inputs and outputs are latched.

The 5-bit control port (Port C) is used for control and

status for the 8-bit, bidirectional bus port (Port A).

Bidirectional Bus I/O Control Signal Denition

INTR (INTERRUPT REQUEST)

A high on this output can be used to interrupt the CPU for

both input or output operations. INTR will be set either by the

rising edge of ACK (INTE1 = 1) or the rising edge of STB

(INTE2 = 1). INTR will be reset by the falling edge of WR (if

previously set by the rising edge or ACK), the falling edge of

RD (if previously set by the rising edge of STB), or the falling

edge of WR when immediately following a low RD pulse or

the falling edge of RD when immediately following a low WR

pulse (if previously set by the rising edges of both ACK and

STB).

Output Operations

OBF (OUTPUT BUFFER FULL)

The OBF output will go “low” to indicate that the CPU has

written data out to Port A.

ACK (ACKNOWLEDGE)

A “low” on this input enables the three-state output buffer of

Port A to send out the data. Otherwise, the output buffer will

be in the high impedance state.

INTE 1 (THE INTE FLIP-FLOP ASSOCIATED WITH OBF)

Controlled by Bit Set/Reset of PC6.

Input Operations

STB (STROBE INPUT)

A “low” on this input loads data into the input latch.

IBF (INPUT BUFFER FULL F/F)

A “high” on this output indicates that data has been loaded

into the input latch.

INTE 2 (THE INTE FLIP-FLOP ASSOCIATED WITH IBF)

Controlled by Bit Set/Reset of PC4.

D7 D6 D5 D4 D3 D2 D1 D0

1

CONTROL WORD

0

1/0 1/0 1/0

PC2 - PC0

1 = INPUT

0 = OUTPUT

PORT B

1 = INPUT

0 = OUTPUT

GROUP B MODE

0 = MODE 0

1 = MODE 1

FIGURE 20. MODE CONTROL WORD

INTE

2

PC7

PC6

PC3

PC2- PC0

WR

8

STB A

IBF A

INTR A

I/O

3

RD

PC7

PC6

OBF A

ACK A

INTE

1

PA7- PA0

FIGURE 21. MODE 2 (BIDIRECTIONAL)

WR

OBF

INTR

ACK

STB

IBF

PERIPHERAL

BUS

RD

DATA FROM CPU

TO HS-82C55ARH

TWHOL

TSLIH

TKHOL

TKLKH

DATA FROM PERI-

PHERAL TO

DATA FROM

HS-82C55ARH

TO PERIPHERAL

DATA FROM

HS-82C55ARH

TO CPU

TSLSH

TKLPV

TKHPX

TPVSH

TSHPX

TRHIL

NOTE: Any sequence where WR occurs before ACK and STB

occurs before RD is permissible.

FIGURE 22. MODE 2 (BIDIRECTIONAL)

HS-82C55ARH

相关PDF资料 |

PDF描述 |

|---|---|

| 59K16A-102T4 | CABLE TERMINATED, FEMALE, RF CONNECTOR, CRIMP, JACK |

| 59K16A-106T4 | CABLE TERMINATED, FEMALE, RF CONNECTOR, CRIMP, JACK |

| 59K16A-109T4 | CABLE TERMINATED, FEMALE, RF CONNECTOR, CRIMP, JACK |

| 59K16A-1M4T4 | CABLE TERMINATED, FEMALE, RF CONNECTOR, CRIMP, JACK |

| 59K28H-102A4 | CABLE TERMINATED, FEMALE, RF CONNECTOR, CRIMP, JACK |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 5962R9583301VFA | 功能描述:LVDS 接口集成电路 RoHS:否 制造商:Texas Instruments 激励器数量:4 接收机数量:4 数据速率:155.5 Mbps 工作电源电压:5 V 最大功率耗散:1025 mW 最大工作温度:+ 85 C 封装 / 箱体:SOIC-16 Narrow 封装:Reel |

| 5962R9583301VZA | 功能描述:LVDS 接口集成电路 RoHS:否 制造商:Texas Instruments 激励器数量:4 接收机数量:4 数据速率:155.5 Mbps 工作电源电压:5 V 最大功率耗散:1025 mW 最大工作温度:+ 85 C 封装 / 箱体:SOIC-16 Narrow 封装:Reel |

| 5962R9660301VXC2732 | 制造商:Intersil Corporation 功能描述:- Bulk |

| 5962R9662202VXC | 制造商:INTER 功能描述: 制造商:INTERC 功能描述: |

| 5962R9665102VXC | 制造商:Intersil Corporation 功能描述: |

发布紧急采购,3分钟左右您将得到回复。