- 您现在的位置:买卖IC网 > PDF目录157280 > 5962R9855201QXA 32-BIT, 12 MHz, RISC MICROCONTROLLER, CPGA144 PDF资料下载

参数资料

| 型号: | 5962R9855201QXA |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 12 MHz, RISC MICROCONTROLLER, CPGA144 |

| 封装: | CERAMIC, PGA-144 |

| 文件页数: | 19/64页 |

| 文件大小: | 1464K |

| 代理商: | 5962R9855201QXA |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页

26

Useful in the control of external subsystem hardware, the

output discrete function is fully static and remains unchanged

until rewritten. Outputs can drive standard (i.e., sink or source)

TTL loads. These outputs three-state on the assertion of the

TEST input pin. Figure 23 shows the timing relationships for

a write to the output discrete bus.

5.2 Discrete Inputs

Status register bits DI1 and DI2, bits 8 and 3 respectively,

reflect the stimulus applied to the input pins. In a system

application the software would make decisions based on the

state (i.e., logic one or zero) of either or both of these bits. The

system software would poll the Status Register by executing

an Input Register Instruction INR Rd,SW; the software then

proceeds to perform a test bit on the appropriate bit (i.e., 3 or

8). The result of the test bit determines the next task performed

by the software. Section 7.0 discusses an example of using a

discrete input to control program for entering the monitor

program. Both DI1 and DI2 input buffers have pull-down

resistors and can float if not in use. 6.0 Interrupts

6.0 Interrupts

The UT69R000 has 15 levels of internal interrupt prioritizing.

Upon the occurrence of an enabled non-masked interrupt, the

UT69R000 program flow (i.e., instruction counter) transfers to

the appropriate interrupt vector. The interrupt vector points to

an interrupt service routine. After completing the interrupt

service routine the program flow is returned to the main

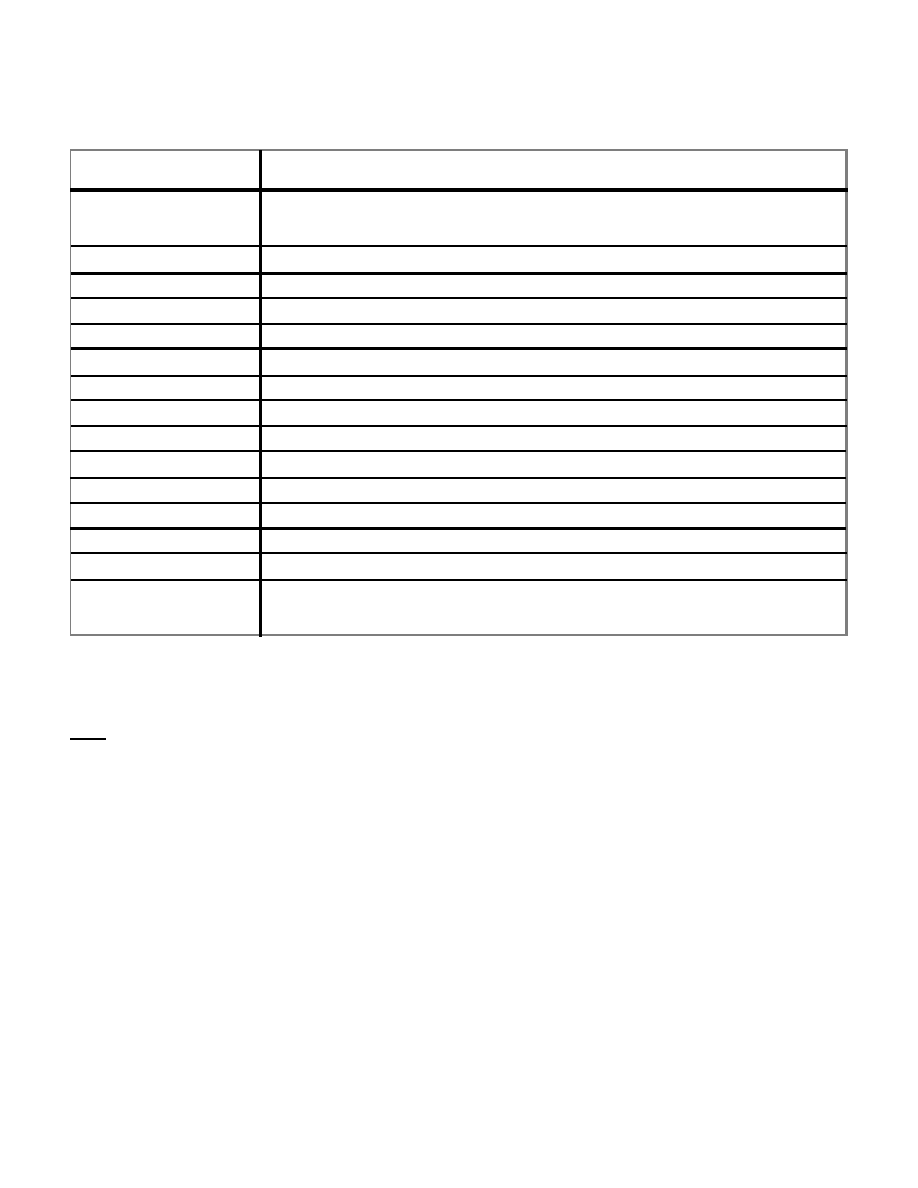

program location. Table 1 shows a list of UT69R000 interrupts.

6.1 Interrupt Control

The Pending Interrupt Register, Mask Register, Status

Register, and Fault Register control and report interrupt

processing. These registers contain the following interrupt

information:

- Interrupt events (PI)

- Interrupt status, masked versus unmasked (MK)

- Interrupt status, enabled versus disabled

(STATUS bit 9)

- Machine error interrupts (FT)

Table 1. Interrupt Definitions

INTERRUPT

NUMBER

0

(Highest

Priority)

1

2

3

4

5

6

7

8

9

10

11

12

DESCRIPTION

Power-Down Interrupt.Cannot be masked or disabled.

Machine Error. Cannot bedisabled.

INT0. External user interrupt.

Software interrupt (USR3)

Fixed-point overflow.(V bit)

Software interrupt (USR2)

Software interrupt (USR1)

Timer A (If implemented).

INT1. External user interrupt.

Timer B (If implemented).

INT2. External user interrupt.

INT3. External user interrupt.

INT4. External user interrupt.

INT6. External user interrupt.

13

14

(Lowest

Priority)

INT5. External user interrupt.

相关PDF资料 |

PDF描述 |

|---|---|

| 5962R9855201VXX | 32-BIT, 12 MHz, RISC MICROCONTROLLER, CPGA144 |

| 5962-9855201QZX | 32-BIT, 12 MHz, RISC MICROCONTROLLER, CQFP132 |

| 5962-9855202QZX | 32-BIT, 16 MHz, RISC MICROCONTROLLER, CQFP132 |

| 5962F9855201QZA | 32-BIT, 12 MHz, RISC MICROCONTROLLER, CQFP132 |

| 5962F9855202QYC | 32-BIT, 16 MHz, RISC MICROCONTROLLER, CQFP132 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 5962R9863601VGA | 制造商:Analog Devices 功能描述: |

| 5962R9863602VGA | 制造商:Analog Devices 功能描述:OP AMP, JFET-INPUT - Rail/Tube |

| 5962R9863701VGA | 制造商:Analog Devices 功能描述:- Rail/Tube |

| 5962R9863701VHA | 制造商:Analog Devices 功能描述:AEROSPACE LOW INPUT CURRENT OPERATIONAL AMPLIFIER - Rail/Tube |

| 5962R9863701VPA | 制造商:Analog Devices 功能描述:OP AMP, GENERAL PURPOSE - Rail/Tube |

发布紧急采购,3分钟左右您将得到回复。