- 您现在的位置:买卖IC网 > PDF目录360408 > 74AHCT377 (NXP Semiconductors N.V.) Octal D-type flip-flop with data enable; positive-edge trigger(带数据使能的八D触发器;上升沿触发;三态) PDF资料下载

参数资料

| 型号: | 74AHCT377 |

| 厂商: | NXP Semiconductors N.V. |

| 英文描述: | Octal D-type flip-flop with data enable; positive-edge trigger(带数据使能的八D触发器;上升沿触发;三态) |

| 中文描述: | 八路D型触发器数据使触发器,积极边缘触发器(带数据使能的八?触发器,上升沿触发,三态) |

| 文件页数: | 2/20页 |

| 文件大小: | 93K |

| 代理商: | 74AHCT377 |

2000 Aug 15

2

Philips Semiconductors

Product specification

Octal D-type flip-flop with data enable;

positive-edge trigger

74AHC377; 74AHCT377

FEATURES

ESD protection:

HBM EIA/JESD22-A114-A exceeds 2000 V

MM EIA/JESD22-A115-A exceeds 200 V

CDM EIA/JESD22-C101 exceeds 1000 V

Balanced propagation delays

All inputs have Schmitt-trigger actions

Inputs accept voltages higher than V

CC

Ideal for addressable register applications

Data enable for address and data synchronization

Eight positive-edge triggered D-type flip-flops

See “273” for master reset version

See “373” for transparent latch version

See “374” for 3-state version

For AHC only: operates with CMOS input levels

For AHCT only: operates with TTL input levels

Specified from

40 to +85 and from

40 to +125

°

C.

DESCRIPTION

The 74AHC/AHCT377 D-type flip-flops are high-speed

silicon-gate CMOS devices and are pin compatible with

low power Schottky TTL (LSTTL). They are specified in

compliance with JEDEC standard No. 7A.

The 74AHC/AHCT377 devices have eight edge-triggered,

D-type flip-flops with individual D inputs and Q outputs.

A common clock (CP) input loads all flip-flops

simultaneously when the data enable (E) is LOW. The

state of each D input, one set-up time before the

LOW-to-HIGH clock transition, is transferred to the

corresponding output (Q

n

) of the flip-flop.

TheE input must be stable only one set-up time prior to the

LOW-to-HIGH transition for predictable operation.

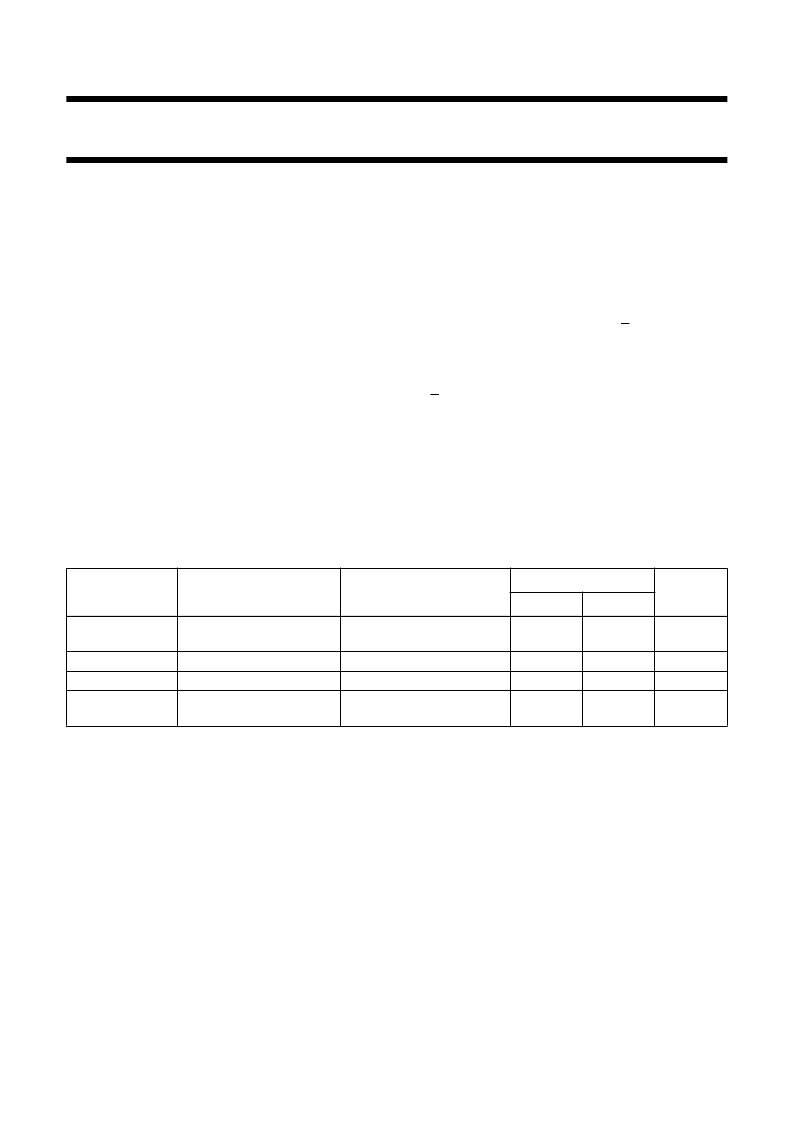

QUICK REFERENCE DATA

GND = 0 V; T

amb

= 25

°

C; t

r

= t

f

≤

3.0 ns.

Notes

1.

C

PD

is used to determine the dynamic power dissipation (P

D

in

μ

W).

P

D

= C

PD

×

V

CC2

×

f

i

+

∑

(C

L

×

V

CC2

×

f

o

) where:

f

i

= input frequency in MHz;

f

o

= output frequency in MHz;

∑

(C

L

×

V

CC2

×

f

o

) = sum of outputs;

C

L

= output load capacitance in pF;

V

CC

= supply voltage in Volts.

The condition is V

I

= GND to V

CC

.

2.

SYMBOL

PARAMETER

CONDITIONS

TYPICAL

UNIT

AHC

AHCT

t

PHL

/t

PLH

propagation delay;

CP to Q

n

maximum clock frequency

input capacitance

power dissipation

capacitance

C

L

= 15 pF; V

CC

= 5 V

3.9

4.0

ns

f

max

C

I

C

PD

C

L

= 15 pF; V

CC

= 5 V

V

I

= V

CC

or GND

C

L

= 50 pF; f = 1 MHz;

notes 1 and 2

175

3.0

20

140

3.0

23

MHz

pF

pF

相关PDF资料 |

PDF描述 |

|---|---|

| 74AHCT541 | Octal buffer/line driver; 3-state(八通道缓冲器/线驱动器;三态;) |

| 74AHC541 | Octal buffer/line driver; 3-state |

| 74AHC541PWDH | Octal buffer/line driver; 3-state |

| 74AHCT573 | Octal D-type transparent latch;3-state(八D透明锁存器;三态) |

| 74AHC573 | Quadruple 2-Input Positive-NAND Gates With Open-Drain Outputs 14-SOIC -40 to 85 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 74AHCT377D | 功能描述:触发器 OCT D-TYPE EDGE TRIGGER RoHS:否 制造商:Texas Instruments 电路数量:2 逻辑系列:SN74 逻辑类型:D-Type Flip-Flop 极性:Inverting, Non-Inverting 输入类型:CMOS 输出类型: 传播延迟时间:4.4 ns 高电平输出电流:- 16 mA 低电平输出电流:16 mA 电源电压-最大:5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:X2SON-8 封装:Reel |

| 74AHCT377D,112 | 功能描述:触发器 OCT D-TYPE EDGE RoHS:否 制造商:Texas Instruments 电路数量:2 逻辑系列:SN74 逻辑类型:D-Type Flip-Flop 极性:Inverting, Non-Inverting 输入类型:CMOS 输出类型: 传播延迟时间:4.4 ns 高电平输出电流:- 16 mA 低电平输出电流:16 mA 电源电压-最大:5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:X2SON-8 封装:Reel |

| 74AHCT377D,118 | 功能描述:触发器 OCT D-TYPE EDGE RoHS:否 制造商:Texas Instruments 电路数量:2 逻辑系列:SN74 逻辑类型:D-Type Flip-Flop 极性:Inverting, Non-Inverting 输入类型:CMOS 输出类型: 传播延迟时间:4.4 ns 高电平输出电流:- 16 mA 低电平输出电流:16 mA 电源电压-最大:5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:X2SON-8 封装:Reel |

| 74AHCT377D-Q100J | 制造商:NXP Semiconductors 功能描述:74AHCT377D-Q100/SO20/REEL13// - Tape and Reel 制造商:NXP Semiconductors 功能描述:IC FLIP FLOP OCTAL D POS 20SOIC |

| 74AHCT377D-T | 功能描述:触发器 OCT D-TYPE EDGE TRIGGER RoHS:否 制造商:Texas Instruments 电路数量:2 逻辑系列:SN74 逻辑类型:D-Type Flip-Flop 极性:Inverting, Non-Inverting 输入类型:CMOS 输出类型: 传播延迟时间:4.4 ns 高电平输出电流:- 16 mA 低电平输出电流:16 mA 电源电压-最大:5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:X2SON-8 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。