- 您现在的位置:买卖IC网 > PDF目录360409 > 74ALS10AD (NXP SEMICONDUCTORS) Triple 3-Input NAND gate PDF资料下载

参数资料

| 型号: | 74ALS10AD |

| 厂商: | NXP SEMICONDUCTORS |

| 元件分类: | 通用总线功能 |

| 英文描述: | Triple 3-Input NAND gate |

| 中文描述: | ALS SERIES, TRIPLE 3-INPUT NAND GATE, PDSO14 |

| 封装: | PLASTIC, SO-14 |

| 文件页数: | 4/7页 |

| 文件大小: | 86K |

| 代理商: | 74ALS10AD |

Philips Semiconductors

Product specification

74ALS10A

Triple 3-input NAND gate

1991 Feb 08

4

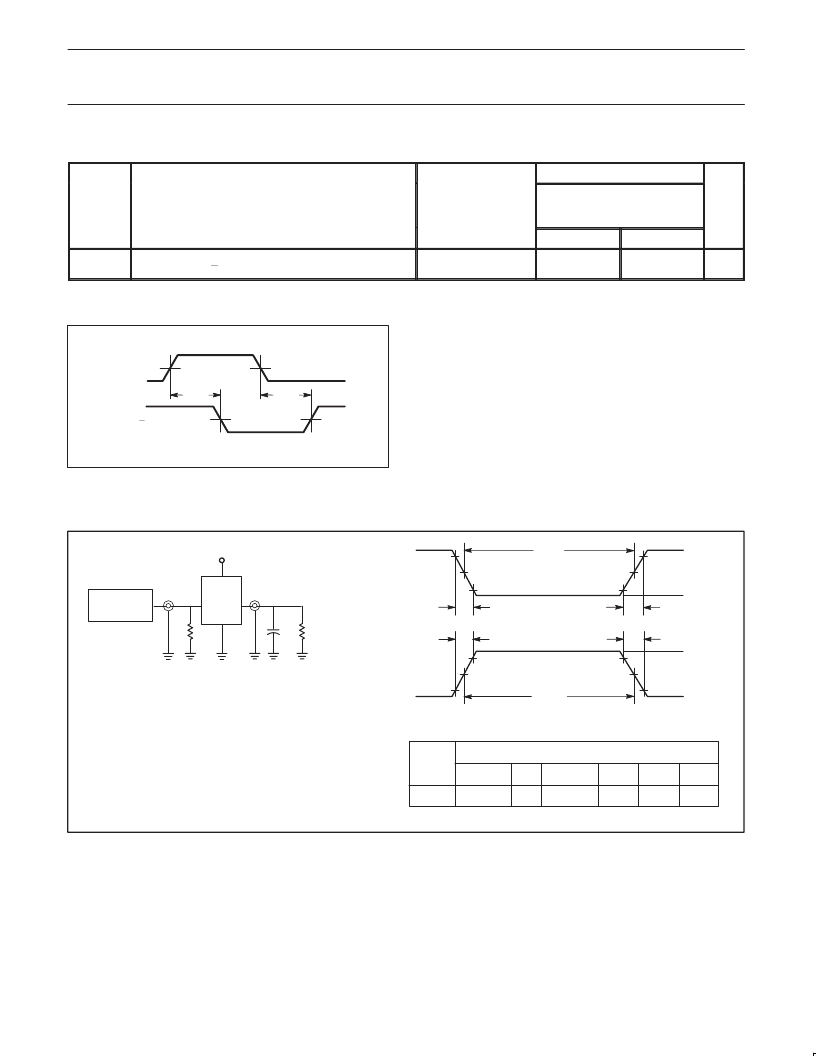

AC ELECTRICAL CHARACTERISTICS

LIMITS

SYMBOL

PARAMETER

TEST CONDITION

T

amb

= 0

°

C to +70

°

C

V

= +5.0V

±

10%

C

L

= 50pF, R

L

= 500

UNIT

MIN

MAX

t

PLH

t

PHL

Propagation delay

nA, nB, nC to nY

Waveform 1

2.0

2.0

11.0

10.0

ns

AC WAVEFORMS

For all waveforms, V

M

= 1.3V.

V

M

V

M

V

M

V

M

t

PLH

t

PHL

nA, nB, nC

nY

SC00018

Waveform 1.

Propagation Delay for Data to Output

TEST CIRCUIT AND WAVEFORMS

t

w

90%

V

M

10%

90%

V

M

10%

90%

V

M

10%

90%

V

M

10%

NEGATIVE

PULSE

POSITIVE

PULSE

t

w

AMP (V)

0.3V

0.3V

t

THL (

t

f

f

)

INPUT PULSE REQUIREMENTS

Rep.Rate

t

w

t

TLH

2.0ns

t

THL

2.0ns

1MHz

500ns

Input Pulse Definition

V

CC

Family

74ALS

D.U.T.

PULSE

GENERATOR

R

L

C

L

R

T

V

IN

V

OUT

Test Circuit for Totem-pole Outputs

DEFINITIONS:

R

L

=

Load resistor;

see AC electrical characteristics for value.

Load capacitance includes jig and probe capacitance;

see AC electrical characteristics for value.

Termination resistance should be equal to Z

OUT

of

pulse generators.

C

L

=

R

T

=

t

THL (

t

f

)

t

TLH (

t

r

)

t

TLH (

t

r

)

AMP (V)

Amplitude

3.5V

1.3V

V

M

SC00005

相关PDF资料 |

PDF描述 |

|---|---|

| 74ALS10AN | Triple 3-Input NAND gate |

| 74ALS112 | Dual J-K negative edge-triggered flip-flop |

| 74ALS112A | Dual J-K negative edge-triggered flip-flop |

| 74ALS112AD | Dual J-K negative edge-triggered flip-flop |

| 74ALS112AN | Dual J-K negative edge-triggered flip-flop |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 74ALS10AN | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:Triple 3-Input NAND gate |

| 74ALS10N | 制造商:NXP Semiconductors 功能描述: |

| 74ALS112 | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:Dual J-K negative edge-triggered flip-flop |

| 74ALS112A | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:Dual J-K negative edge-triggered flip-flop |

| 74ALS112AD | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:Dual J-K negative edge-triggered flip-flop |

发布紧急采购,3分钟左右您将得到回复。