- 您现在的位置:买卖IC网 > PDF目录360417 > 74ALVCH16843 (NXP Semiconductors N.V.) 3-Line To 8-Line Decoders/Demultiplexers 16-SSOP -40 to 85 PDF资料下载

参数资料

| 型号: | 74ALVCH16843 |

| 厂商: | NXP Semiconductors N.V. |

| 英文描述: | 3-Line To 8-Line Decoders/Demultiplexers 16-SSOP -40 to 85 |

| 中文描述: | 18位总线接口D型锁存器三态 |

| 文件页数: | 2/12页 |

| 文件大小: | 84K |

| 代理商: | 74ALVCH16843 |

Philips Semiconductors

Product specification

74ALVCH16843

18-bit bus interface D-type latch (3-State)

2

1998 Aug 04

853–2108 019833

FEATURES

Wide supply voltage range of 1.2V to 3.6V

Complies with JEDEC standard no. 8-1A.

CMOS low power consumption

Direct interface with TTL levels

Current drive

±

24 mA at 3.0 V

MULTIBYTE

TM

flow-through standard pin-out architecture

Low inductance multiple V

CC

and GND pins for minimum noise

and ground bounce

All data inputs have bus hold

Output drive capability 50

transmission lines @ 85

°

C

DESCRIPTION

The 74ALVCH16843 has two 9–bit D-type latch featuring separate

D-type inputs for each latch and 3-State outputs for bus oriented

applications. The two sections of each register are controlled

independently by the latch enable (nLE), clear (nCLR),

preset (nPRE) and output enable (nOE) control gates.

When nOE is LOW, the data in the registers appear at the outputs.

When nOE is HIGH, the outputs are in the high impedance OFF

state. Operation of the nOE input does not affect the state of the

flip-flops.

The 74ALVCH16843 has active bus hold circuitry which is provided

to hold unused or floating data inputs at a valid logic level. This

feature eliminates the need for external pull-up or pull-down

resistors.

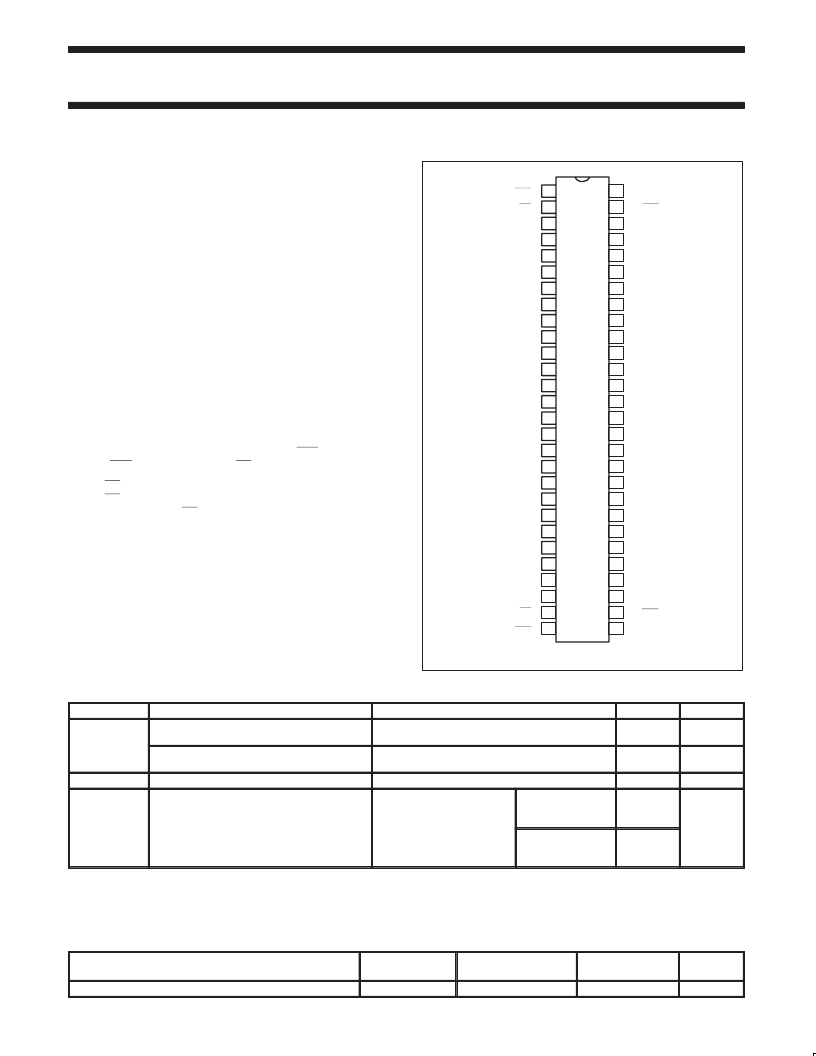

PIN CONFIGURATION

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

1OE

1Q

0

1Q

1

1Q

2

1Q

3

1Q

4

1Q

5

GND

V

CC

GND

1Q

6

1Q

7

1Q

8

2Q

0

2Q

1

2Q

2

GND

2Q

3

2Q

4

2Q

5

V

CC

2Q

6

2Q

7

GND

2Q

8

2CLR

1D

0

GND

1D

1

1D

2

V

CC

1D

3

1D

4

1D

5

GND

1D

6

1D

7

1D

8

2D

0

2D

1

2D

2

GND

2D

3

2D

4

2D

5

V

CC

2D

6

2D

7

GND

2D

8

2LE

1PRE

1CLR

2OE

1LE

2PRE

SH00143

QUICK REFERENCE DATA

GND = 0V; T

amb

= 25

°

C; t

r

= t

f

≤

2.5ns

SYMBOL

Propagation delay

nDn to nQn

Propagation delay

nLE to nQn

C

I

Input capacitance

PARAMETER

CONDITIONS

TYPICAL

2.2

2.1

2.3

2.0

5.0

UNIT

t

PHL

/t

PLH

V

CC

= 2.5V, C

L

= 30pF

V

CC

= 3.3V, C

L

= 50pF

V

CC

= 2.5V, C

L

= 30pF

V

CC

= 3.3V, C

L

= 50pF

ns

ns

pF

C

PD

Power dissipation capacitance per buffer

Power dissi ation ca acitance er buffer

V

I

= GND to V

CC1

transparent mode

Output enabled

Output disabled

Clocked mode

Output enabled

Output disabled

17

3

pF

19

9

NOTES:

1. C

PD

is used to determine the dynamic power dissipation (P

D

in

μ

W):

P

D

= C

PD

×

V

CC2

×

f

i

+ (C

L

×

V

CC2

×

f

o

) where: f

i

= input frequency in MHz; C

L

= output load capacitance in pF;

f

o

= output frequency in MHz; V

CC

= supply voltage in V; (C

L

×

V

CC2

×

f

o

) = sum of outputs.

ORDERING INFORMATION

PACKAGES

TEMPERATURE

RANGE

–40

°

C to +85

°

C

OUTSIDE NORTH

AMERICA

74ALVCH16843 DGG

NORTH AMERICA

DRAWING

NUMBER

SOT364-1

56-Pin Plastic Thin Shrink Small Outline (TSSOP) Type II

ACH16843 DGG

相关PDF资料 |

PDF描述 |

|---|---|

| 74ALVCH16952 | 16-bit registered transceiver 3-State |

| 74ALVCH32501 | 3-Line To 8-Line Decoders/Demultiplexers 16-PDIP -40 to 85 |

| 74ALVCH32501EC | 36-bit universal bus transceiver with direction pin; 5 V tolerant; 3-state |

| 74ALVCHS162830 | 18-bit to 36-bit address driver with bus hold (3-State) |

| 74ALVCHS162830DGB | 18-bit to 36-bit address driver with bus hold (3-State) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 74ALVCH16843APA | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Integrated Device Technology Inc 功能描述: |

| 74ALVCH16843DG | 功能描述:闭锁 18BIT BUS INTER LTCH/SET RESET RoHS:否 制造商:Micrel 电路数量:1 逻辑类型:CMOS 逻辑系列:TTL 极性:Non-Inverting 输出线路数量:9 高电平输出电流: 低电平输出电流: 传播延迟时间: 电源电压-最大:12 V 电源电压-最小:5 V 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:SOIC-16 封装:Reel |

| 74ALVCH16843DGG | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:18-bit bus-interface D-type latch 3-State |

| 74ALVCH16843DGG,11 | 功能描述:闭锁 18BIT BUS INTER RoHS:否 制造商:Micrel 电路数量:1 逻辑类型:CMOS 逻辑系列:TTL 极性:Non-Inverting 输出线路数量:9 高电平输出电流: 低电平输出电流: 传播延迟时间: 电源电压-最大:12 V 电源电压-最小:5 V 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:SOIC-16 封装:Reel |

| 74ALVCH16843DGG,112 | 制造商:NXP Semiconductors 功能描述: |

发布紧急采购,3分钟左右您将得到回复。