- 您现在的位置:买卖IC网 > PDF目录298541 > 74HCT4510DB (NXP SEMICONDUCTORS) BCD up/down counter PDF资料下载

参数资料

| 型号: | 74HCT4510DB |

| 厂商: | NXP SEMICONDUCTORS |

| 元件分类: | 计数器 |

| 英文描述: | BCD up/down counter |

| 中文描述: | HCT SERIES, SYN POSITIVE EDGE TRIGGERED 4-BIT BIDIRECTIONAL DECADE COUNTER, PDSO16 |

| 文件页数: | 5/12页 |

| 文件大小: | 102K |

| 代理商: | 74HCT4510DB |

December 1990

2

Philips Semiconductors

Product specication

BCD up/down counter

74HC/HCT4510

FEATURES

Output capability: standard

ICC category: MSI

GENERAL DESCRIPTION

The 74HC/HCT4510 are high-speed Si-gate CMOS

devices and are pin compatible with the “4510” of the

“4000B” series. They are specified in compliance with

JEDEC standard no. 7A.

The 74HC/HCT4510 are edge-triggered synchronous

up/down BCD counters with a clock input (CP), an

up/down count control input (UP/DN), an active LOW

count enable input (CE), an asynchronous active HIGH

parallel load input (PL), four parallel inputs (D0 to D3), four

parallel outputs (Q0 to Q3), an active LOW terminal count

output (TC), and an overriding asynchronous master reset

input (MR).

Information on D0 to D3 is loaded into the counter while PL

is HIGH, independent of all other input conditions except

the MR input, which must be LOW. With PL LOW, the

counter changes on the LOW-to-HIGH transition of CP if

CE is LOW. UP/DN determines the direction of the count,

HIGH for counting up, LOW for counting down. When

counting up, TC is LOW when Q0 and Q3 are HIGH and CE

is LOW. When counting down, TC is LOW when Q0 to Q3

and CE are LOW. A HIGH on MR resets the counter (Q0 to

Q3 = LOW) independent of all other input conditions.

Logic equation for terminal count:

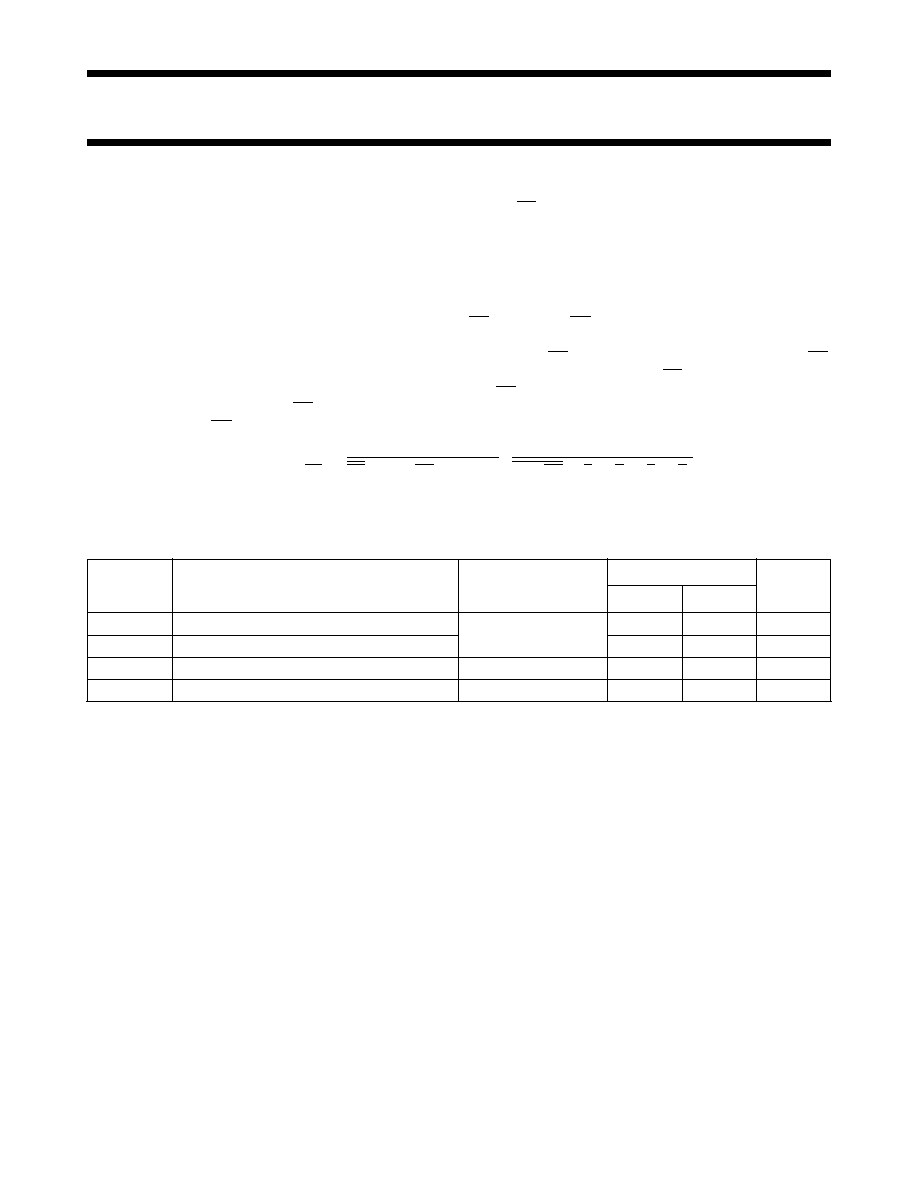

QUICK REFERENCE DATA

GND = 0 V; Tamb =25 °C; tr =tf = 6 ns

Notes

1. CPD is used to determine the dynamic power dissipation (PD in W):

PD =CPD × VCC2 × fi + ∑ (CL × VCC2 × fo) where:

fi = input frequency in MHz

fo = output frequency in MHz

∑ (CL × VCC2 × fo) = sum of outputs

CL = output load capacitance in pF

VCC = supply voltage in V

2. For HC the condition is VI = GND to VCC. For HCT the condition is VI = GND to VCC 1.5 V

ORDERING INFORMATION

See

“74HC/HCT/HCU/HCMOS Logic Package Information”.

SYMBOL

PARAMETER

CONDITIONS

TYPICAL

UNIT

HC

HCT

tPHL/ tPLH

propagation delay CP to Qn

CL = 15 pF; VCC = 5 V 2123ns

fmax

maximum clock frequency

57

58

MHz

CI

input capacitance

3.5

pF

CPD

power dissipation capacitance per package

notes 1 and 2

50

53

pF

TC = CE . {(UP/DN) . Q

0 .Q3 +(UP/DN) . Q0 .Q1 .Q2 .Q3 }

相关PDF资料 |

PDF描述 |

|---|---|

| 74HCT4510N | BCD up/down counter |

| 74HCT4510PW | BCD up/down counter |

| 74LS197PC | LS SERIES, SYN NEGATIVE EDGE TRIGGERED 4-BIT UP BINARY COUNTER, PDIP14 |

| 74LV138PWDH-T | LV/LV-A/LVX/H SERIES, OTHER DECODER/DRIVER, INVERTED OUTPUT, PDSO16 |

| 74LVC162640ADL-T | LVC/LCX/Z SERIES, DUAL 8-BIT TRANSCEIVER, INVERTED OUTPUT, PDSO48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 74HCT4511D | 功能描述:编码器、解码器、复用器和解复用器 BCD-7SEG LCH/DEC/DVR RoHS:否 制造商:Micrel 产品:Multiplexers 逻辑系列:CMOS 位数: 线路数量(输入/输出):2 / 12 传播延迟时间:350 ps, 400 ps 电源电压-最大:2.625 V, 3.6 V 电源电压-最小:2.375 V, 3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-44 封装:Tray |

| 74HCT4511D,652 | 功能描述:编码器、解码器、复用器和解复用器 BCD-7SEG LCH/DEC/DVR RoHS:否 制造商:Micrel 产品:Multiplexers 逻辑系列:CMOS 位数: 线路数量(输入/输出):2 / 12 传播延迟时间:350 ps, 400 ps 电源电压-最大:2.625 V, 3.6 V 电源电压-最小:2.375 V, 3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-44 封装:Tray |

| 74HCT4511D,653 | 功能描述:编码器、解码器、复用器和解复用器 BCD TO 7 SEG LATCH/DECODR/DEVR RoHS:否 制造商:Micrel 产品:Multiplexers 逻辑系列:CMOS 位数: 线路数量(输入/输出):2 / 12 传播延迟时间:350 ps, 400 ps 电源电压-最大:2.625 V, 3.6 V 电源电压-最小:2.375 V, 3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-44 封装:Tray |

| 74HCT4511N | 功能描述:编码器、解码器、复用器和解复用器 BCD TO 7 SEG LATCH DECODR/DEVR RoHS:否 制造商:Micrel 产品:Multiplexers 逻辑系列:CMOS 位数: 线路数量(输入/输出):2 / 12 传播延迟时间:350 ps, 400 ps 电源电压-最大:2.625 V, 3.6 V 电源电压-最小:2.375 V, 3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-44 封装:Tray |

| 74HCT4511N,652 | 功能描述:编码器、解码器、复用器和解复用器 BCD TO 7 SEG LATCH RoHS:否 制造商:Micrel 产品:Multiplexers 逻辑系列:CMOS 位数: 线路数量(输入/输出):2 / 12 传播延迟时间:350 ps, 400 ps 电源电压-最大:2.625 V, 3.6 V 电源电压-最小:2.375 V, 3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-44 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。