- 您现在的位置:买卖IC网 > PDF目录1888 > 78P2352-IELR/F (Maxim Integrated Products)IC LIU SDH SONET 2CH 128-LQFP PDF资料下载

参数资料

| 型号: | 78P2352-IELR/F |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 11/42页 |

| 文件大小: | 0K |

| 描述: | IC LIU SDH SONET 2CH 128-LQFP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 1,000 |

| 类型: | 线路接口装置(LIU) |

| 驱动器/接收器数: | 2/2 |

| 规程: | E4,OC-3,STM1-E |

| 电源电压: | 3.15 V ~ 3.45 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 128-LQFP 裸露焊盘 |

| 供应商设备封装: | 128-LQFP-EP(14x14) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页

78P2352

Dual Channel

OC-3/ STM1-E/ E4 LIU

Page: 19 of 42

2006 Teridian Semiconductor Corporation

Rev. 2.4

PIN DESCRIPTION (CONTINUED)

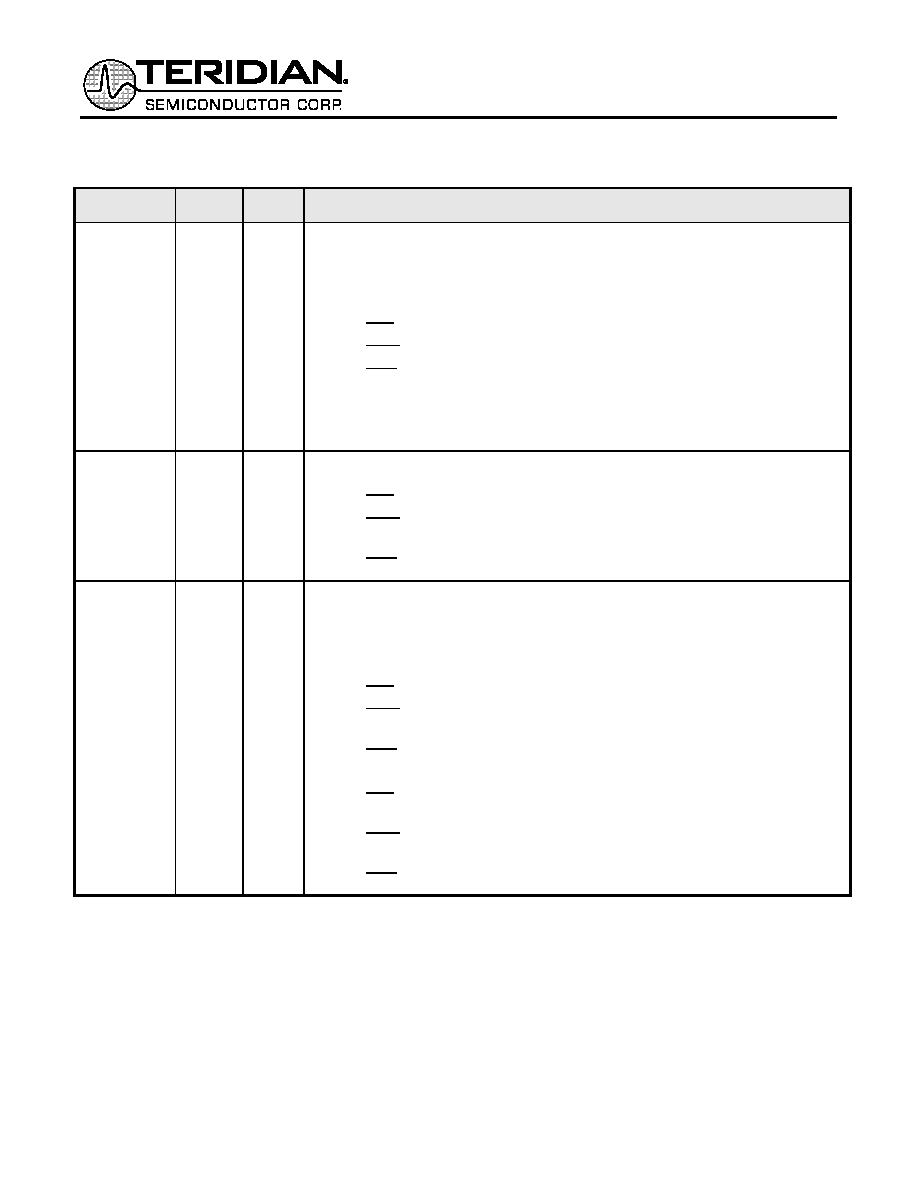

CONTROL PINS

NAME

PIN

TYPE

DESCRIPTION

FRST

78

CIT

FIFO Phase-Initialization Control:

When asserted, the transmit FIFO pointers are reset to the respective

“centered” states. Also resets the FIERR interrupt bit. De-assertion edge of

FRSTx will resume FIFO operation.

Low: Channel 1 FRST assertion

Float: Normal operation

High: Channel 2 FRST assertion

Because the internal VCO clock and off-chip transmit clocks may not be

stable during transmit power-up, it is recommended to always reset the FIFOs

after powering up the IC or the transmitter.

Not valid during Plesiochronous Serial Mode.

LPBKx

17, 18

CIT

Analog Loopback Selection:

Low: Normal operation

Float: Remote Loopback Enable: Recovered receive data and clock

are looped back to the transmitter for retransmission.

High: Local Loopback Enable: The serial transmit data is looped back

and used as the input to the receiver.

CKMODE

15

CIT

Clock Mode Selection:

Selects the method of inputting transmit data into the chip. See

TRANSMITTER OPERATION section for more information.

In PARALLEL mode (SDI_PAR high):

Low: Parallel transmit clock is input to the 78P2352.

Float: Parallel transmit clock is input to the 78P2352. Loop-timing

mode enabled.

High: Parallel transmit clock is output from the 78P2352

In SERIAL mode (SDI_PAR low):

Low: Reference clock is synchronous to transmit clock and data.

Data is clocked in with SIxCKP/N and passed through a FIFO

Float: Reference clock is synchronous to transmit data. Clock is

recovered with a CDR and data is passed through a FIFO

High: Reference clock is plesiochronous to transmit data. Clock is

recovered with a CDR and the FIFO is bypassed

相关PDF资料 |

PDF描述 |

|---|---|

| 78Q2120C09-64CGTR/F | TXRX 10/100 BASE 3.3V 64-LQFP |

| 78Q2133/F | TXRX 10/100 MDIX 3.3V IND 32-QFN |

| 78Q8392LA03-28CHR/F | TXRX 10BASE 2/5 ETH COAX 28-PLCC |

| 78Q8430-100IGT/F | IC LAN MEDIA ACCESS CTLR 100LQFP |

| A1020B-1CQ84C | IC FPGA 2K GATES 84-CQFP COM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 78P2352-IGT | 制造商:TERIDIAN 制造商全称:TERIDIAN 功能描述:Dual Channel OC-3/ STM1-E/ E4 LIU |

| 78P2352-IGT/F | 功能描述:接口 - 专用 Dual Ch OC-3/STM1-1e/E4 LIU RoHS:否 制造商:Texas Instruments 产品类型:1080p60 Image Sensor Receiver 工作电源电压:1.8 V 电源电流:89 mA 最大功率耗散: 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:BGA-59 |

| 78P2352-IGTR | 功能描述:接口 - 专用 Dual Ch OC-3/STM1-1e/E4 LIU RoHS:否 制造商:Texas Instruments 产品类型:1080p60 Image Sensor Receiver 工作电源电压:1.8 V 电源电流:89 mA 最大功率耗散: 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:BGA-59 |

| 78P2352-IGTR/F | 功能描述:接口 - 专用 Dual Ch OC-3/STM1-1e/E4 LIU RoHS:否 制造商:Texas Instruments 产品类型:1080p60 Image Sensor Receiver 工作电源电压:1.8 V 电源电流:89 mA 最大功率耗散: 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:BGA-59 |

| 78P236-IP | 制造商:SSI 功能描述: |

发布紧急采购,3分钟左右您将得到回复。