- 您现在的位置:买卖IC网 > PDF目录223059 > 840002AGT (INTEGRATED DEVICE TECHNOLOGY INC) 226.67 MHz, OTHER CLOCK GENERATOR, PDSO16 PDF资料下载

参数资料

| 型号: | 840002AGT |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | XO, clock |

| 英文描述: | 226.67 MHz, OTHER CLOCK GENERATOR, PDSO16 |

| 封装: | 4.40 X 5 MM, 0.92 MM HEIGHT, MO-153, TSSOP-16 |

| 文件页数: | 12/13页 |

| 文件大小: | 808K |

| 代理商: | 840002AGT |

Integrated

Circuit

Systems, Inc.

840002AG

www.icst.com/products/hiperclocks.html

REV. B FEBRUARY 17, 2006

8

ICS840002

FEMTOCLOCKSCRYSTAL-TO-

LVCMOS/LVTTL FREQUENCY SYNTHESIZER

LAYOUT GUIDELINE

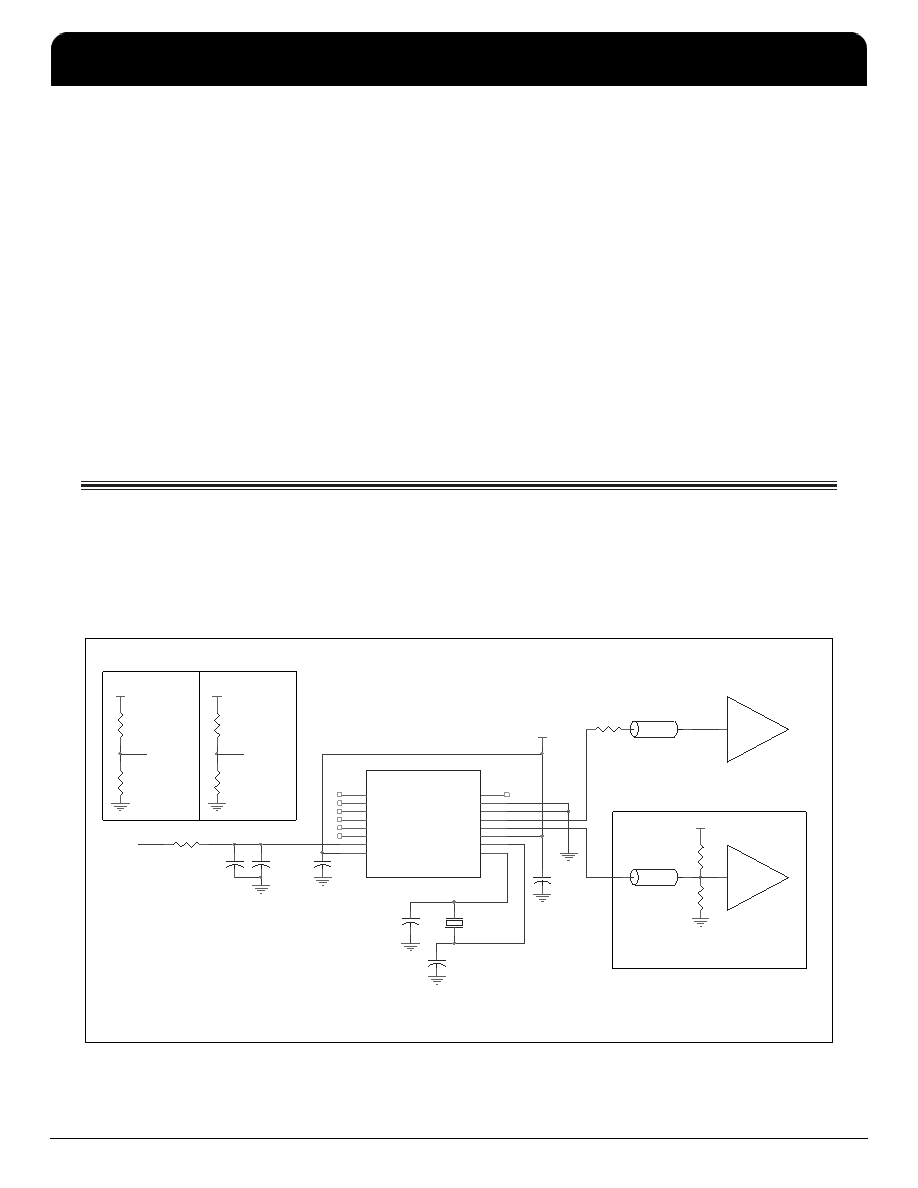

Figure 3 shows a schematic example of the ICS840002. An

example of LVCMOS termination is shown in this schematic.

Additional LVCMOS termination approaches are shown in the

LVCMOS Termination Application Note. In this example, an 18

pF parallel resonant 26.5625MHz crystal is used. The C1=22pF

FIGURE 3. ICS840002 SCHEMATIC EXAMPLE

and C2=22pF are recommended for frequency accuracy. For

different board layout, the C1 and C2 may be slightly adjusted

for optimizing frequency accuracy. 1K

Ω pullup or pulldown re-

sistors can be used for the logic control input pins.

To Logic

Input

pins

RU2

Not Install

C2

22pF

VDD

RD2

1K

LVCMOS

C5

0.1u

RU1

1K

Zo = 50 Ohm

Unused output can be left floating. There should

no trace attached to unused output. Device

characterized with all outputs terminated.

C1

22pF

Set Logic

Input to

'0'

VDDA

VDD

U1

ICS840002

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

FSEL0

XTAL_SEL

TEST_CLK

OE

MR

nPLL_SEL

VDDA

VDD

XTAL_OUT

XTAL_IN

VDDO

Q1

Q0

GND

FSEL1

Logic Control Input Examples

Optional Termination

RD1

Not Install

X1

If not using the crystal input, it can be left floating.

For additional protection the XTAL_IN pin can be

tied to ground.

C4

0.01u

Set Logic

Input to

'1'

C3

10uF

R4

100

VDD

XTAL2

To Logic

Input

pins

XTAL1

R2

33

R3

100

R1

10

C6

0.1u

Zo = 50 Ohm

VDD

LVCMOS

INPUTS:

CRYSTAL INPUT:

For applications not requiring the use of the crystal oscillator

input, both XTAL_IN and XTAL_OUT can be left floating.

Though not required, but for additional protection, a 1k

Ω

resistor can be tied from XTAL_IN to ground.

TEST_CLK INPUT:

For applications not requiring the use of the test clock, it can

be left floating. Though not required, but for additional

protection, a 1k

Ω resistor can be tied from the TEST_CLK to

ground.

LVCMOS CONTROL PINS:

All control pins have internal pull-ups or pull-downs; additional

resistance is not required but can be added for additional

protection. A 1k

Ω resistor can be used.

RECOMMENDATIONS FOR UNUSED INPUT AND OUTPUT PINS

OUTPUTS:

LVCMOS OUTPUT:

All unused LVCMOS output can be left floating. We

recommend that there is no trace attached.

ICS840002

FEMTOCLOCKS CRYSTAL-TO-LVCMOS/LVTTL FREQUENCY SYNTHESIZER

TSD

IDT / ICS FEMTOCLOCKS CRYSTAL-TO-LVCMOS/LVTTL FREQUENCY SYNTHESIZER

ICS840002

8

相关PDF资料 |

PDF描述 |

|---|---|

| 840002AG | 226.67 MHz, OTHER CLOCK GENERATOR, PDSO16 |

| 8400110EKILF | OTHER CLOCK GENERATOR, QCC32 |

| 84013036 | INTERCONNECTION DEVICE |

| 8403612LX | 2K X 8 STANDARD SRAM, 70 ns, CDIP24 |

| 841 | FEMALE, D SUBMINIATURE CONNECTOR, IDC, RECEPTACLE |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 840002AL | 制造商:ICS 制造商全称:ICS 功能描述:FEMTOCLOCKS? CRYSTAL-TO LVCMOS/ |

| 840-00323 | 制造商:LG Corporation 功能描述:HINGE UPPER PART |

| 840-00324 | 制造商:LG Corporation 功能描述:HINGE, LOCK |

| 840-004 | 功能描述:罩类、盒类及壳类产品 2.5/4mm sq. 5 pole terminal RoHS:否 制造商:Bud Industries 产品:Boxes 外部深度:6.35 mm 外部宽度:6.35 mm 外部高度:2.56 mm NEMA 额定值: IP 等级: 材料:Acrylonitrile Butadiene Styrene (ABS) 颜色:Red |

| 84000421 | 制造商:GUNTHER SPELSBERG 功能描述:TERMINAL BLOCK |

发布紧急采购,3分钟左右您将得到回复。