- 您现在的位置:买卖IC网 > PDF目录24617 > 9161A-01CW16LF (INTEGRATED DEVICE TECHNOLOGY INC) 120 MHz, VIDEO CLOCK GENERATOR, PDSO16 PDF资料下载

参数资料

| 型号: | 9161A-01CW16LF |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 120 MHz, VIDEO CLOCK GENERATOR, PDSO16 |

| 封装: | LEAD FREE, SOIC-16 |

| 文件页数: | 13/15页 |

| 文件大小: | 544K |

| 代理商: | 9161A-01CW16LF |

7

ICS9161A

0210I—03/21/05

Power Management Issues

Power-down mode 1

The ICS9161A contains a mechanism to reduce the

quiescent power when stand-by operation is desired.

Power-down mode 1 is invoked by polling PD# low and

having the proper CNTL register bit set to zero. In this

mode, VCOs are shut down, the VCLK output is forced

high, and the MCLK output is set to a user-defined low

frequency value to refresh dynamic RAM.

The power-down MCLK value is determined by the following

equation:

MCLKPD = FREF/(PWRDWN register divisor value)

The power-down register divisor is determined according

to the 4-bit word programmed into the PWRDWN register

(see table below).

Power-down mode 2

When there is no need for any output during power-down,

an alternate mode is available which will completely shut

down all outputs and the reference oscillator, but still

preserves all register contents. Power-down mode 2 in

invoked by first programming the power-down bit in the

CNTL register and then pulling the PD# pin low.

The PD# pin

The PD# pin has a standard internal pull-up resistor during

normal operation. When the chip goes into power-down

mode 1 or 2, the normal pull-up resistor is dynamically

switched to a weak pull-up, which reduces power

consumption. If the PD# pin is allowed to float after it has

been

pulled

down, the weak pull-up will bring the signal high and allow

the device to resume operation.

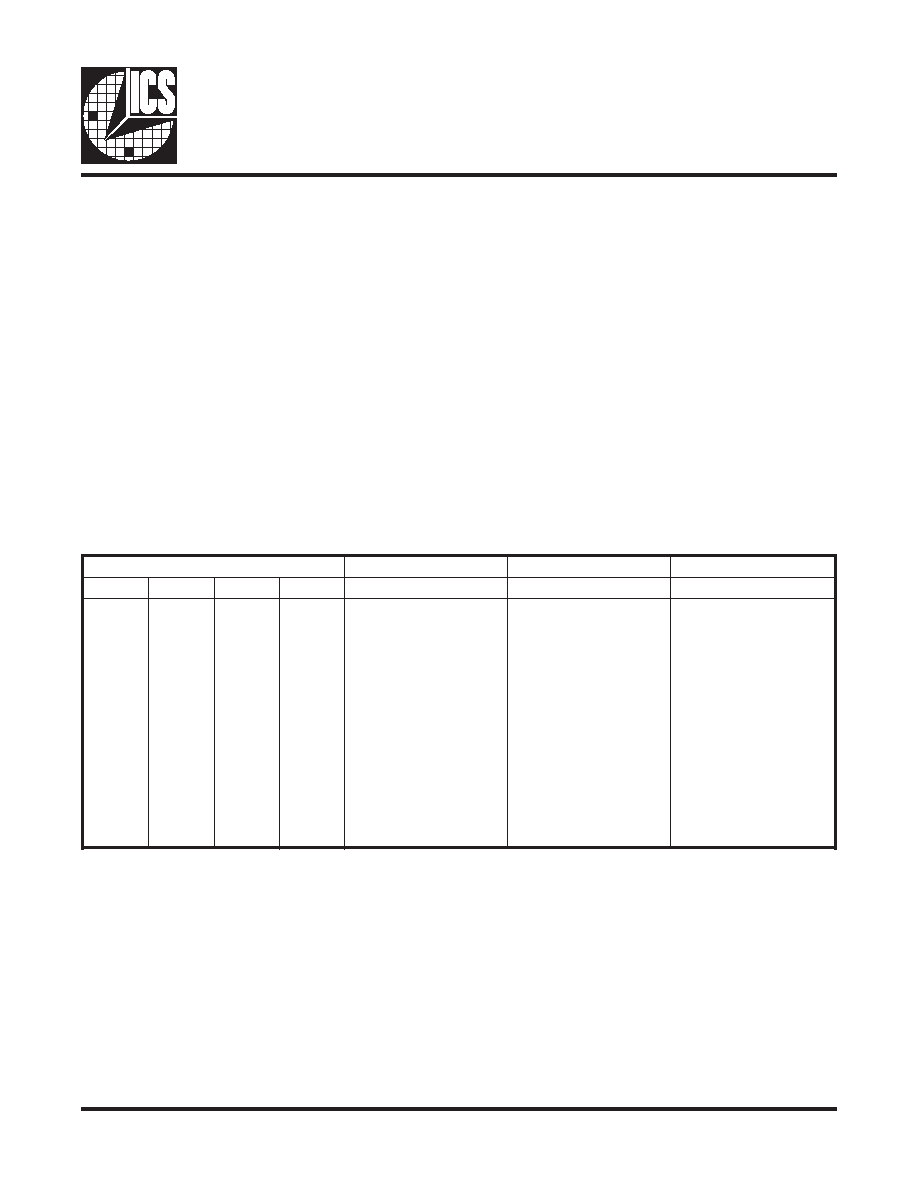

Power-Down Register Table

s

t

i

b

N

W

D

R

W

PN

W

D

R

W

Pn

w

o

d

-

r

e

w

o

PD

P

K

L

C

M

3

P2

P1

P0

Pe

u

l

a

V

r

e

t

s

i

g

e

Rr

o

s

i

v

i

Df

(

F

E

R

)

8

1

8

1

3

.

4

1

=

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

2

3

4

5

6

7

)

t

l

u

a

f

e

d

(

8

9

A

B

C

D

E

F

a

/

n

2

3

0

3

8

2

6

2

4

2

0

2

8

1

6

1

4

1

2

1

0

1

8

6

4

a

/

n

z

H

k

4

.

7

4

z

H

k

3

.

7

4

z

H

k

4

.

1

5

z

H

k

7

.

0

5

z

H

k

6

.

6

9

5

z

H

k

8

.

0

5

6

z

H

k

9

.

5

1

7

z

H

k

5

.

5

9

7

z

H

k

9

.

4

9

8

z

H

M

2

0

.

1

z

H

M

9

1

.

1

z

H

M

3

4

.

1

z

H

M

9

7

.

1

z

H

M

9

3

.

2

z

H

M

8

5

.

3

相关PDF资料 |

PDF描述 |

|---|---|

| 051-427-3196 | RF Coaxial Connectors |

| 9161A-01CW16WLF | 120 MHz, VIDEO CLOCK GENERATOR, PDSO16 |

| 9161A-01CW16W | 120 MHz, VIDEO CLOCK GENERATOR, PDSO16 |

| 9162C | 2M X 32 FAST PAGE DRAM MODULE, 60 ns, SMA72 |

| 9163901MFA | QUAD LINE DRIVER, CDFP16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 9161A-01CW16LFT | 功能描述:时钟发生器及支持产品 PC SPECIAL PURPOSE RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| 9-161A-R | 制造商:Cinch Connectors 功能描述: |

| 9161-CHR-BULK | 制造商:Belden Inc 功能描述: |

| 9-161-L | 制造商:Cinch Connectors 功能描述: |

| 9-161-R | 制造商:Cinch Connectors 功能描述:Conn Terminal Strip 9 POS 11.13mm Crimp ST Cable Mount |

发布紧急采购,3分钟左右您将得到回复。