- 您现在的位置:买卖IC网 > PDF目录24623 > 9250BF-16-T (INTEGRATED DEVICE TECHNOLOGY INC) 150 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 PDF资料下载

参数资料

| 型号: | 9250BF-16-T |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 150 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 封装: | 0.300 INCH, SSOP-56 |

| 文件页数: | 6/19页 |

| 文件大小: | 570K |

| 代理商: | 9250BF-16-T |

14

ICS9250-16

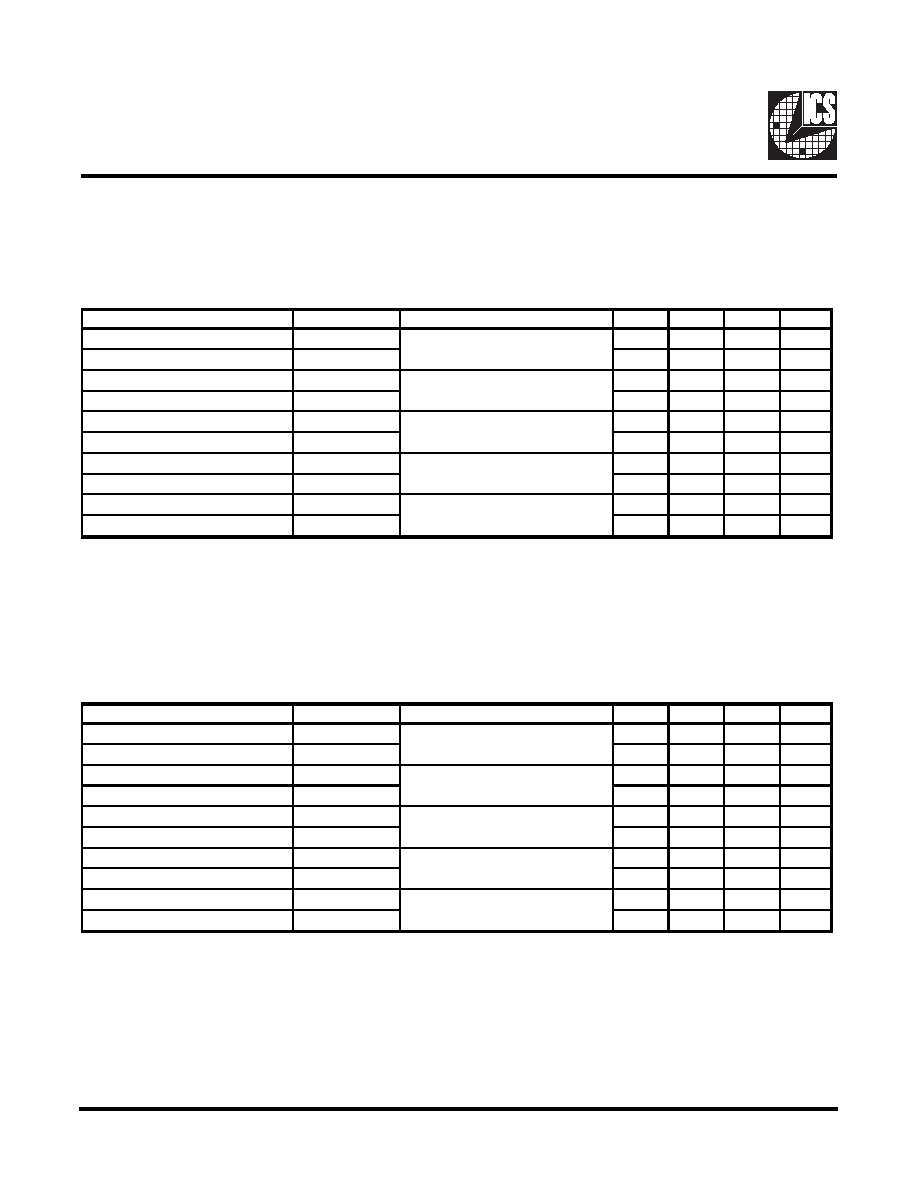

Group Skews (CPU = 66 MHz)

TA = 0 - 70 C; VDD = 3.3 V +/-5%, VDDL = 2.5 V +/-5%

CPU & IOAPIC load (lumped) = 20 pF; PCI, SDRAM, 3V66 load (lumped) = 30 pF

Refer to Group Offset Waveform diagram for definition of transition edges.

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

CPU to SDRAM

Skew

1

Tsk1 CPU-SDRAM

-3

-2.6

-2

ns

Skew Window

1

Tw1 CPU-SDRAM

0

150

500

ps

CPU to 3V66

Skew

1

Tsk1 CPU-3V66

77.2

8

ns

Skew Window

1

Tw1 CPU-3V66

0

130

500

ps

SDRAM to 3V66

Skew

1

Tsk1 SDRAM-3V66

-500

100

500

ps

Skew Window

1

Tw1 SDRAM-3V66

0

155

500

ps

3V66 to PCI

Skew

1

Tsk1 3V66-PCI

1.5

2.4

3.5

ns

Skew Window

1

Tw1 3V66-PCI

0

275

500

ps

IOAPIC to PCI

Skew

1

Tsk1 IOAPIC-PCI

-1

-0.4

1

ns

Skew Window

1

Tw1 IOAPIC-PCI

00.25

1

ns

1Guaranteed by design, not 100% tested in production.

CPU @ 1.25 V, SDRAM @ 1.5 V

CPU @ 1.25 V, 3V66 @ 1.5 V

SDRAM, 3V66 @ 1.5 V

3V66, PCI @ 1.5 V

IOAPIC @ 1.25 V, PCI @ 1.5 V

Group Skews (CPU = 100 MHz)

TA = 0 - 70 C; VDD = 3.3 V +/-5%, VDDL = 2.5 V +/-5%

CPU & IOAPIC load (lumped) = 20 pF; PCI, SDRAM, 3V66 load (lumped) = 30 pF

Refer to Group Offset Waveform diagram for definition of transition edges.

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

CPU to SDRAM

Skew

1

Tsk2 CPU-SDRAM

4.5

4.9

5.5

ns

Skew Window

1

Tw2 CPU-SDRAM

0

140

500

ps

CPU to 3V66

Skew

1

Tsk2 CPU-3V66

4.5

4.8

5.5

ns

Skew Window

1

Tw2 CPU-3V66

0

150

500

ps

SDRAM to 3V66

Skew

1

Tsk2 SDRAM-3V66

-500

100

500

ps

Skew Window

1

Tw2 SDRAM-3V66

0

155

500

ps

3V66 to PCI

Skew

1

Tsk2 3V66-PCI

1.5

2.4

3.5

ns

Skew Window

1

Tw2 3V66-PCI

0

275

500

ps

IOAPIC to PCI

Skew

1

Tsk2 IOAPIC-PCI

-1

-0.4

1

ns

Skew Window

1

Tw2 IOAPIC-PCI

00.25

1

ns

1Guaranteed by design, not 100% tested in production.

CPU @ 1.25 V, SDRAM @ 1.5 V

CPU @ 1.25 V, 3V66 @ 1.5 V

SDRAM, 3V66 @ 1.5 V

3V66, PCI @ 1.5 V

IOAPIC @ 1.25 V, PCI @ 1.5 V

相关PDF资料 |

PDF描述 |

|---|---|

| 9250BF-16 | 150 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 9250BF-16LF-T | 150 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 9250BF-27 | 133 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 9250BF-27LFT | 133 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 051-928-9029 | RF Coaxial Connectors |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 9250BF27LF | 制造商:Integrated Device Technology Inc 功能描述:PLL Frequency Generator Dual 56-Pin SSOP Tube |

| 9250BF-27LF | 功能描述:时钟发生器及支持产品 RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| 9250BF-27LFT | 功能描述:时钟发生器及支持产品 RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| 9250BF-28LF | 制造商:Integrated Device Technology Inc 功能描述:PLL Frequency Generator Single 56-Pin SSOP Tube |

| 9250BF-28LFT | 制造商:Integrated Device Technology Inc 功能描述:PLL Frequency Generator Single 56-Pin SSOP T/R |

发布紧急采购,3分钟左右您将得到回复。