- 您现在的位置:买卖IC网 > PDF目录122717 > 935263686557 (NXP SEMICONDUCTORS) 6 CHANNEL(S), 200M bps, SERIAL COMM CONTROLLER, PQFP64 PDF资料下载

参数资料

| 型号: | 935263686557 |

| 厂商: | NXP SEMICONDUCTORS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 6 CHANNEL(S), 200M bps, SERIAL COMM CONTROLLER, PQFP64 |

| 封装: | 10 X 10 MM, 1.40 MM HEIGHT, PLASTIC, SOT-314-2, LQFP-64 |

| 文件页数: | 17/22页 |

| 文件大小: | 170K |

| 代理商: | 935263686557 |

Philips Semiconductors

Preliminary specification

PDI1394P11A

3-port physical layer interface

1999 Mar 10

4

6.0

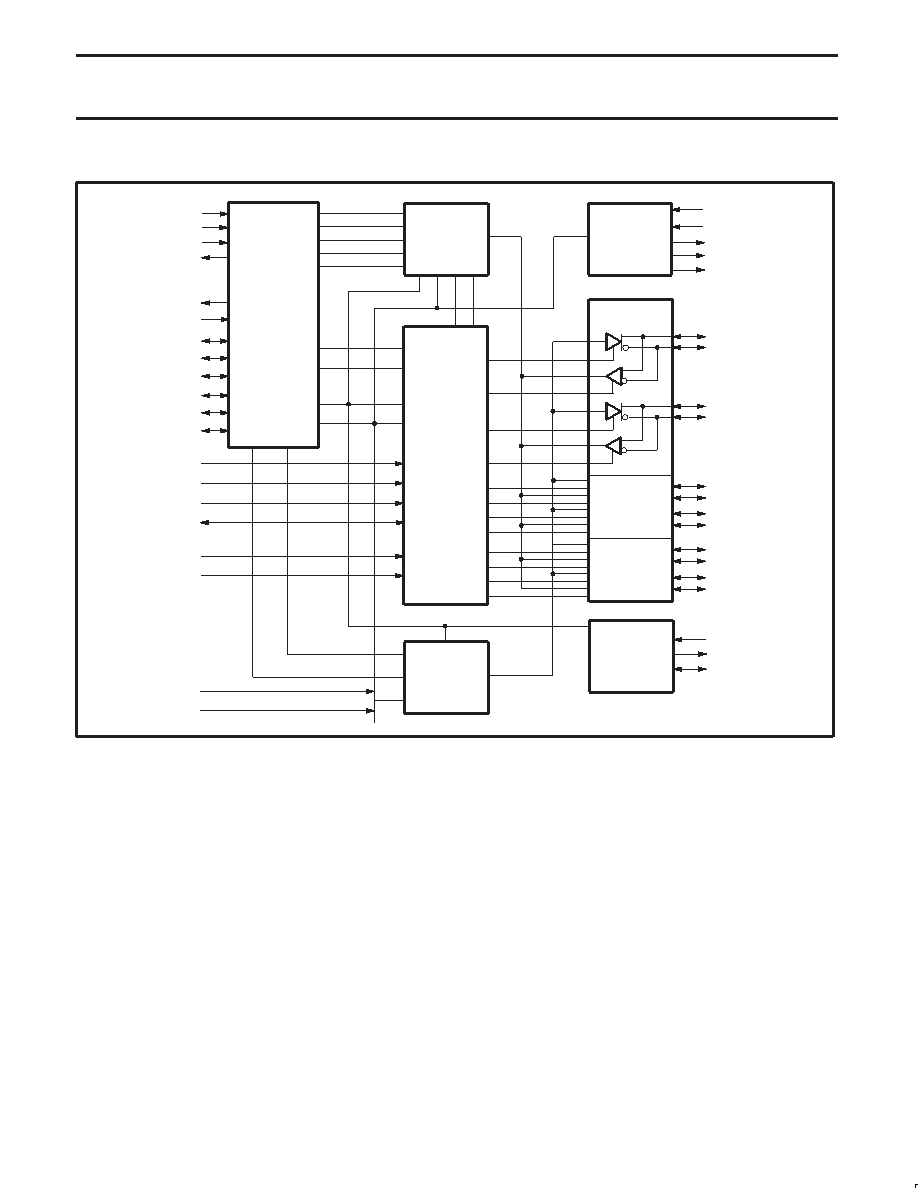

BLOCK DIAGRAM

PORT 1

PORT 2

PORT 3

BIAS

VOLTAGE AND

CURRENT

GENERATOR

RECEIVED

DATA

DECODER/

TIMER

LINK

INTERFACE

ARBITRATION

AND CONTROL

STATE

MACHINE

LOGIC

CRYSTAL

OSCILLATOR

PLL SYSTEM

& TRANSMIT

CLOCK

GENERATOR

TRANSMIT

DATA

ENCODER

TESTM1

TESTM2

C/LKON

PC0

PC1

PC2

D0

D1

D2

D3

CTL0

CTL1

LREQ

SYSCLK

CNA

ISO–

LPS

CPS

RESET–

PD

R0

R1

TPBIAS1

TPBIAS2

TPBIAS3

TPA1+

TPA1–

TPB1+

TPB1–

TPA2+

TPA2–

TPB2+

TPB2–

TPA3+

TPA3–

TPB3+

TPB3–

XI

XO

FILTER

SV00228

7.0

FUNCTIONAL SPECIFICATION

The PDI1394P11A is an IEEE1394–1995 High Performance Serial

Bus Specification compliant physical layer interface device. It

provides an interface between an attached link layer controller and

three 1394 cable interface ports. In addition to the interface function,

the PDI1394P11A performs bus initialization and arbitration

functions as well as monitoring line conditions and connection

status.

7.1

Clocking

The PDI1394P11A utilizes a stable internal reference clock of

196.608 MHz. The reference clock is generated using an external

24.576 MHz crystal and an internal Phase Locked Loop (PLL). The

PLL clock is divided down to 49.152 MHz and 98.304 MHz clock

signals. The 49.152 MHz clock is used for internal logic and

provided as an output to clock a link layer controller. The 196.608

MHz and 98.304 MHz clocks are used for synchronization of the

transmitted strobe and data information.

7.2

Port Interfaces

The PDI1394P11A provides the transceiver functions needed to

implement a three port node in a cable-based 1394 network. Each

cable port incorporates two differential line transceivers. In addition

to transmission and reception of packet data, the line transceivers

monitor conditions on the cable to determine connection status, data

speed, and bus arbitration states.

The PDI1394P11A receives data to be transmitted over the bus from

two or four parallel data paths to the Link Controller, D[0:3]. These

data paths are latched and synchronized with the 49.152 MHz clock.

The parallel bit paths are combined serially, encoded and

transmitted at either 98.304 Mb/s or 196.608 Mb/s, depending

whether the transaction is a 100 Mb/s or 200 Mb/s transfer,

respectively. The transmitted data is encoded as data-strobe

information, with the data information being transmitted on the TPB

cable pairs and the strobe information transmitted on the TPA cable

pairs.

During packet reception the TPA and TPB transmitters of the

receiving cable port are disabled, and the receivers for that port are

enabled. The encoded data information is received on the TPA cable

pair and the strobe information is received on the TPB cable pair.

The combination of the data and strobe signals is decoded to

recover the receive clock signal and the serial data stream. The

serial data stream is converted to two or four parallel bit streams,

resynchronized to the internal 49.152 MHz clock and sent to the

相关PDF资料 |

PDF描述 |

|---|---|

| 9173B-01CS08LF | 75 MHz, VIDEO CLOCK GENERATOR, PDSO8 |

| 9212AF-13LF-IN0 | 533.3 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO24 |

| 932S200BFLFT | 133 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 932S203AFLF | 133.3 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 950201AFLFT | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 935264217557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935267356112 | 制造商:NXP Semiconductors 功能描述:IC TEA1507PN |

| 935268081112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935268721125 | 制造商:NXP Semiconductors 功能描述:Buffer/Line Driver 1-CH Non-Inverting 3-ST CMOS 5-Pin TSSOP T/R |

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

发布紧急采购,3分钟左右您将得到回复。