- 您现在的位置:买卖IC网 > PDF目录122717 > 935269195118 (NXP SEMICONDUCTORS) 8 I/O, PIA-GENERAL PURPOSE, PDSO16 PDF资料下载

参数资料

| 型号: | 935269195118 |

| 厂商: | NXP SEMICONDUCTORS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8 I/O, PIA-GENERAL PURPOSE, PDSO16 |

| 封装: | 7.50 MM, PLASTIC, MS-013, SOT-162-1, SO-16 |

| 文件页数: | 10/15页 |

| 文件大小: | 140K |

| 代理商: | 935269195118 |

Philips Semiconductors

Product data

PCA9554/PCA9554A

8-bit I2C and SMBus I/O port with interrupt

2002 Jul 26

4

REGISTERS

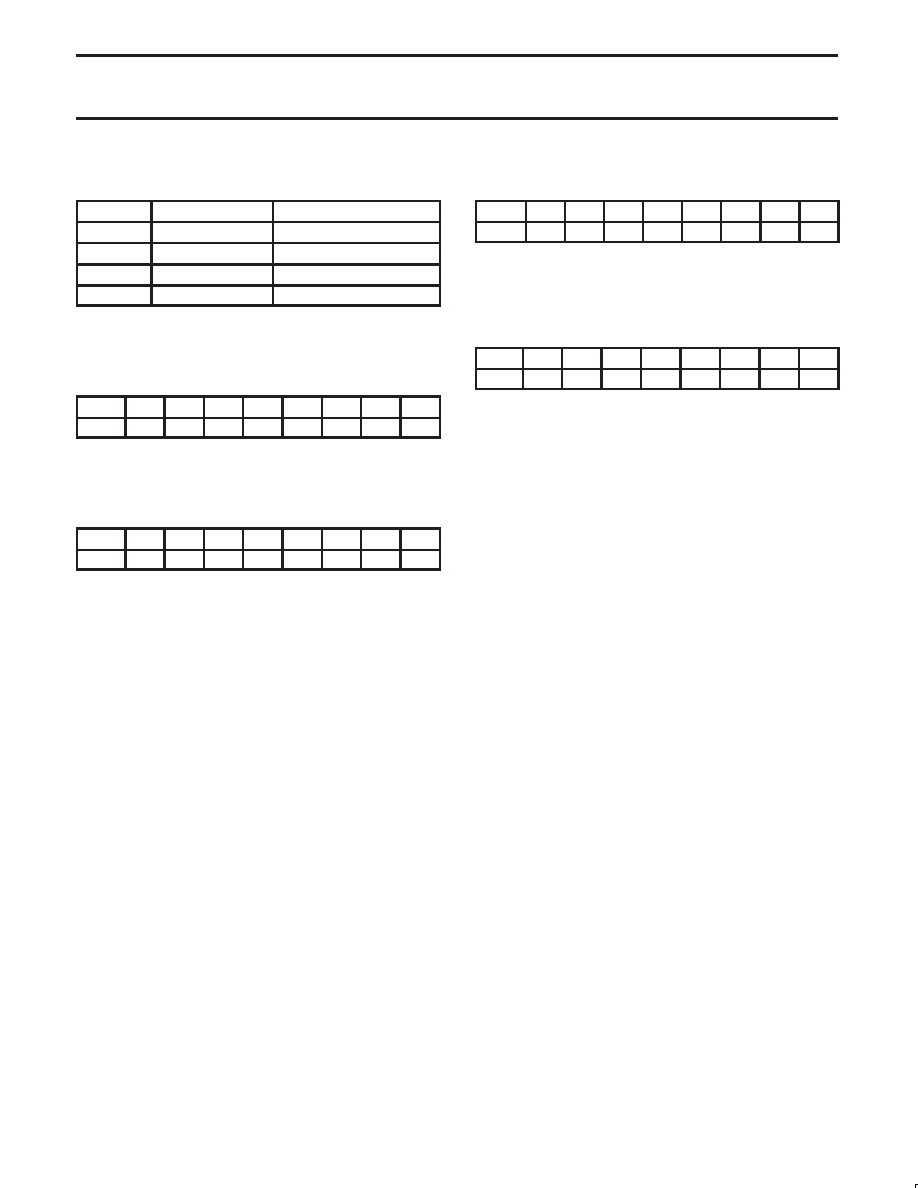

Command Byte

Command

Protocol

Function

0

Read byte

Input port register

1

Read/write byte

Output port register

2

Read/write byte

Polarity inversion register

3

Read/write byte

Configuration register

The command byte is the first byte to follow the address byte during

a write transmission. It is used as a pointer to determine which of the

following registers will be written or read.

Register 0 – Input Port Register

bit

I7

I6

I5

I4

I3

I2

I1

I0

default

1

This register is a read only port. It reflects the incoming logic levels

of the pins, regardless of whether the pin is defined as an input or an

output by Register 3. Writes to this register have no effect.

Register 1 – Output Port Register

bit

O7

O6

O5

O4

O3

O2

O1

O0

default

1

This register reflects the outgoing logic levels of the pins defined as

outputs by Register 3. Bit values in this register have no effect on

pins defined as inputs. Reads from this register return the value that

is in the flip-flop controlling the output selection, NOT the actual pin

value.

Register 2 – Polarity Inversion Register

bit

N7

N6

N5

N4

N3

N2

N1

N0

default

0

This register allows the user to invert the polarity of the Input Port

Register data. If a bit in this register is set (written with ‘1’), the

corresponding Input Port data is inverted. If a bit in this register is

cleared (written with a ‘0’), the Input Port data polarity is retained.

Register 3 – Configuration Register

bit

C7

C6

C5

C4

C3

C2

C1

C0

default

1

This register configures the directions of the I/O pins. If a bit in this

register is set, the corresponding port pin is enabled as an input with

high impedance output driver. If a bit in this register is cleared, the

corresponding port pin is enabled as an output. At reset, the I/Os are

configured as inputs with a weak pull-up to VDD.

Power-on Reset

When power is applied to VDD, an internal power-on reset holds the

PCA9554 in a reset state until VDD has reached VPOR. At that point,

the reset condition is released and the PCA9554 registers and state

machine will initialize to their default states.

Interrupt Output

The open-drain interrupt output is activated when one of the port

pins change state and the pin is configured as an input. The

interrupt is deactivated when the input returns to its previous state or

the input port register is read.

Note that changing an I/O from an output to an input may cause a

false interrupt to occur if the state of the pin does not match the

contents of the input port register.

相关PDF资料 |

PDF描述 |

|---|---|

| 935056380512 | 8 CHANNEL(S), 115.2K bps, SERIAL COMM CONTROLLER, PQCC84 |

| 932S203YGT | 133.3 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 935069310118 | I2C BUS CONTROLLER, PDSO20 |

| 9LRS3187BKLF | 133.33 MHz, PROC SPECIFIC CLOCK GENERATOR, PQCC32 |

| 935262233118 | 16 I/O, PIA-GENERAL PURPOSE, PDSO24 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

| 935269544557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY TDA9587-2US1-V1.3 |

| 935269987557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY TDA9587-1US1-V1.8 SUBBED TO 935269987557 |

| 935270713557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC CHP |

| 935270792551 | 制造商:NXP Semiconductors 功能描述:IC BUFF DVR TRI-ST 16BIT 56VFBGA |

发布紧急采购,3分钟左右您将得到回复。