参数资料

| 型号: | 93AA76C-I/SN |

| 厂商: | Microchip Technology |

| 文件页数: | 10/36页 |

| 文件大小: | 0K |

| 描述: | IC EEPROM 8KBIT 3MHZ 8SOIC |

| 标准包装: | 100 |

| 格式 - 存储器: | EEPROMs - 串行 |

| 存储器类型: | EEPROM |

| 存储容量: | 8K(1K x 8 或 512 x 16) |

| 速度: | 1MHz,2MHz,3MHz |

| 接口: | Microwire 3 线串行 |

| 电源电压: | 1.8 V ~ 5.5 V |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 8-SOIC(0.154",3.90mm 宽) |

| 供应商设备封装: | 8-SOICN |

| 包装: | 管件 |

| 产品目录页面: | 1452 (CN2011-ZH PDF) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页当前第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

�� �

�

�

�93AA76A/B/C,� 93LC76A/B/C,� 93C76A/B/C�

�3.0�

�PIN� DESCRIPTIONS�

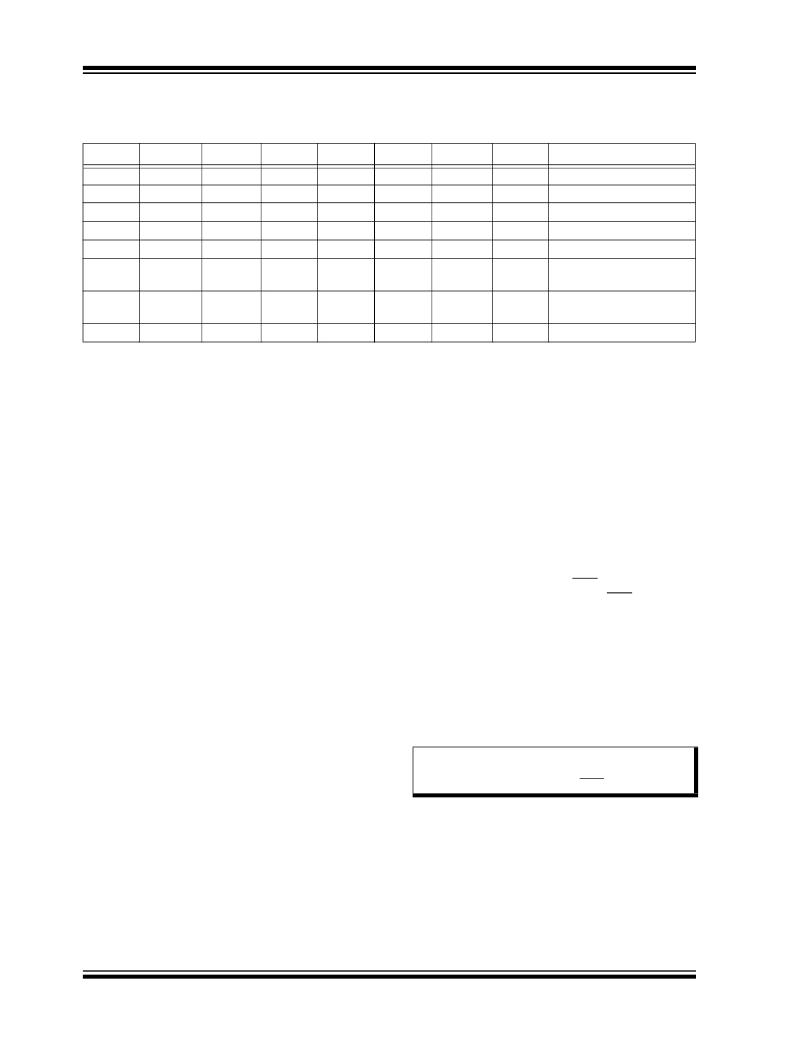

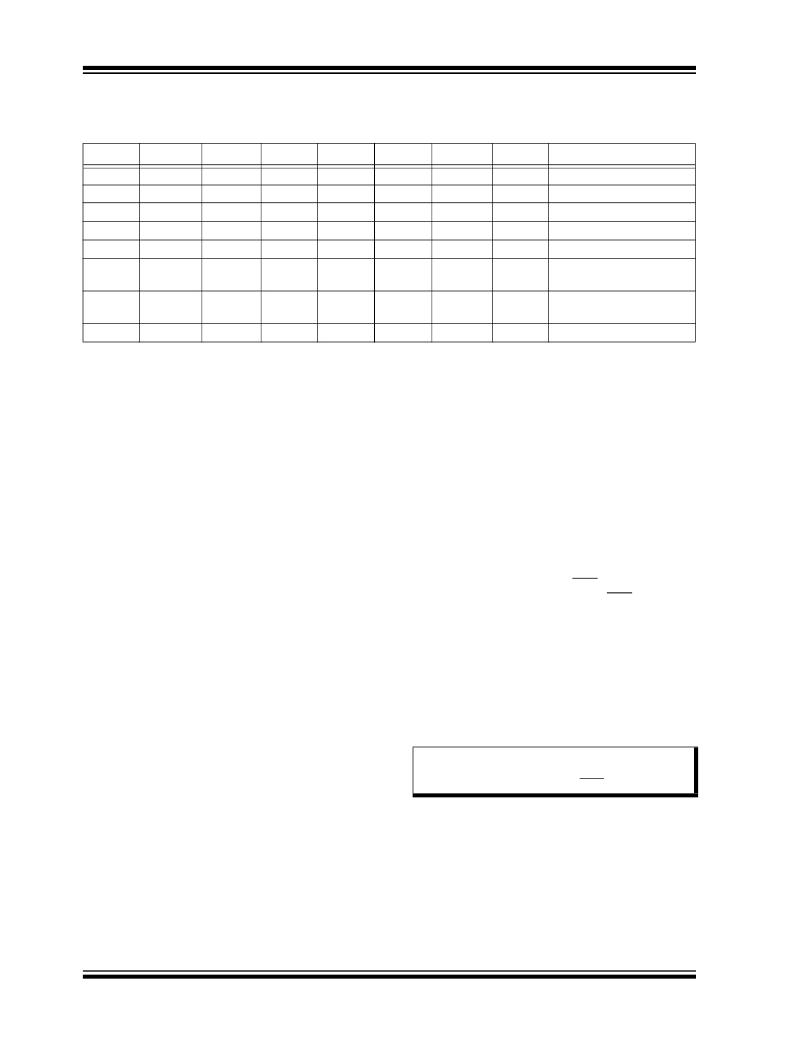

�TABLE� 3-1:�

�PIN� DESCRIPTIONS�

�Name�

�CS�

�CLK�

�DI�

�DO�

�V� SS�

�ORG�

�PDIP�

�1�

�2�

�3�

�4�

�5�

�6�

�SOIC�

�1�

�2�

�3�

�4�

�5�

�6�

�TSSOP�

�1�

�2�

�3�

�4�

�5�

�6�

�MSOP�

�1�

�2�

�3�

�4�

�5�

�6�

�DFN� (1)�

�1�

�2�

�3�

�4�

�5�

�6�

�TDFN� (1)�

�1�

�2�

�3�

�4�

�5�

�6�

�SOT-23�

�5�

�4�

�3�

�1�

�2�

�—�

�Function�

�Chip� Select�

�Serial� Clock�

�Data� In�

�Data� Out�

�Ground�

�Organization/93XX76C�

�only�

�PE�

�7�

�7�

�7�

�7�

�7�

�7�

�—�

�Program� Enable/�

�93XX76C� only�

�V� CC�

�8�

�8�

�8�

�8�

�8�

�8�

�6�

�Power� Supply�

�Note� 1:�

�The� exposed� pad� on� the� DFN/TDFN� package� may� be� connected� to� V� SS� or� left� floating.�

�3.1�

�Chip� Select� (CS)�

�data� bits� before� an� instruction� is� executed.� CLK� and� DI�

�A� high� level� selects� the� device;� a� low� level� deselects�

�the� device� and� forces� it� into� Standby� mode.� However,� a�

�then� become� “don’t� care”� inputs� waiting� for� a� new� Start�

�condition� to� be� detected.�

�programming� cycle� that� is� already� in� progress� will� be�

�completed,� regardless� of� the� Chip� Select� (CS)� input�

�3.3�

�Data� In� (DI)�

�signal.� If� CS� is� brought� low� during� a� program� cycle,� the�

�device� will� go� into� Standby� mode� as� soon� as� the�

�programming� cycle� is� completed.�

�Data� In� (DI)� is� used� to� clock� in� a� Start� bit,� opcode,�

�address� and� data� synchronously� with� the� CLK� input.�

�CS� must� be� low� for� 250� ns� minimum� (T� CSL� )� between�

�3.4�

�Data� Out� (DO)�

�consecutive� instructions.� If� CS� is� low,� the� internal�

�control� logic� is� held� in� a� Reset� status.�

�Data� Out� (DO)� is� used� in� the� Read� mode� to� output� data�

�synchronously� with� the� CLK� input� (T� PD� after� the�

�3.2�

�Serial� Clock� (CLK)�

�positive� edge� of� CLK).�

�This� pin� also� provides� Ready/� Busy� status� information�

�The� Serial� Clock� is� used� to� synchronize� the� communi-�

�cation� between� a� master� device� and� the� 93XX� series�

�device.� Opcodes,� address� and� data� bits� are� clocked� in�

�on� the� positive� edge� of� CLK.� Data� bits� are� also� clocked�

�out� on� the� positive� edge� of� CLK.�

�CLK� can� be� stopped� anywhere� in� the� transmission�

�sequence� (at� high� or� low-level)� and� can� be� continued�

�anytime� with� respect� to� Clock� High� Time� (T� CKH� )� and�

�Clock� Low� Time� (T� CKL� ).� This� gives� the� controlling�

�master� freedom� in� preparing� opcode,� address� and�

�during� erase� and� write� cycles.� Ready/� Busy� status� infor-�

�mation� is� available� on� the� DO� pin� if� CS� is� brought� high�

�after� being� low� for� minimum� Chip� Select� Low� Time�

�(T� CSL� )� and� an� erase� or� write� operation� has� been�

�initiated.�

�The� Status� signal� is� not� available� on� DO,� if� CS� is� held�

�low� during� the� entire� erase� or� write� cycle.� In� this� case,�

�DO� is� in� the� High-Z� mode.� If� status� is� checked� after� the�

�erase/write� cycle,� the� data� line� will� be� high� to� indicate�

�the� device� is� ready.�

�data.�

�CLK� is� a� “don’t� care”� if� CS� is� low� (device� deselected).� If�

�CS� is� high,� but� the� Start� condition� has� not� been�

�detected� (DI� =� 0� ),� any� number� of� clock� cycles� can� be�

�received� by� the� device� without� changing� its� status� (i.e.,�

�waiting� for� a� Start� condition).�

�Note:�

�3.5�

�After� a� programming� cycle� is� complete,�

�issuing� a� Start� bit� and� then� taking� CS� low�

�will� clear� the� Ready/� Busy� status� from� DO.�

�Organization� (ORG)�

�CLK� cycles� are� not� required� during� the� self-timed� write�

�(i.e.,� auto� erase/write)� cycle.�

�After� detection� of� a� Start� condition� the� specified� number�

�of� clock� cycles� (respectively,� low-to-high� transitions� of�

�CLK)� must� be� provided.� These� clock� cycles� are�

�required� to� clock� in� all� required� opcode,� address� and�

�DS21796M-page� 10�

�When� the� ORG� pin� is� connected� to� V� CC� or� logic� high,�

�the� (x16)� memory� organization� is� selected.� When� the�

�ORG� pin� is� tied� to� V� SS� or� logic� low,� the� (x8)� memory�

�organization� is� selected.� For� proper� operation,� ORG�

�must� be� tied� to� a� valid� logic� level.�

�93XX76A� devices� are� always� (x8)� organization� and�

�93XX76B� devices� are� always� (x16)� organization.�

�?� 2003-2012� Microchip� Technology� Inc.�

�相关PDF资料 |

PDF描述 |

|---|---|

| 93LC56C-E/P | IC EEPROM 2KBIT 3MHZ 8DIP |

| XC3S50-4VQG100I | SPARTAN-3A FPGA 50K STD 100-VQFP |

| 93C56C-E/P | IC EEPROM 2KBIT 3MHZ 8DIP |

| 93LC56A-E/P | IC EEPROM 2KBIT 3MHZ 8DIP |

| 93LC56B-E/P | IC EEPROM 2KBIT 3MHZ 8DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 93AA76CT-I/MC | 功能描述:电可擦除可编程只读存储器 8k 512X16 OR 1024X8 SER EE 1.8V IND RoHS:否 制造商:Atmel 存储容量:2 Kbit 组织:256 B x 8 数据保留:100 yr 最大时钟频率:1000 KHz 最大工作电流:6 uA 工作电源电压:1.7 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-8 |

| 93AA76CT-I/MNY | 功能描述:电可擦除可编程只读存储器 8k 512X16 OR 1024X8 SER EE 1.8V IND RoHS:否 制造商:Atmel 存储容量:2 Kbit 组织:256 B x 8 数据保留:100 yr 最大时钟频率:1000 KHz 最大工作电流:6 uA 工作电源电压:1.7 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-8 |

| 93AA76CT-I/MS | 功能描述:电可擦除可编程只读存储器 516x8-1024x8 - 1.8V RoHS:否 制造商:Atmel 存储容量:2 Kbit 组织:256 B x 8 数据保留:100 yr 最大时钟频率:1000 KHz 最大工作电流:6 uA 工作电源电压:1.7 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-8 |

| 93AA76CT-I/MSG | 功能描述:电可擦除可编程只读存储器 516x8-1024x8 - 1.8V Lead Free Package RoHS:否 制造商:Atmel 存储容量:2 Kbit 组织:256 B x 8 数据保留:100 yr 最大时钟频率:1000 KHz 最大工作电流:6 uA 工作电源电压:1.7 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-8 |

| 93AA76CT-I/SN | 功能描述:电可擦除可编程只读存储器 516x8-1024x8 - 1.8V RoHS:否 制造商:Atmel 存储容量:2 Kbit 组织:256 B x 8 数据保留:100 yr 最大时钟频率:1000 KHz 最大工作电流:6 uA 工作电源电压:1.7 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-8 |

发布紧急采购,3分钟左右您将得到回复。