参数资料

| 型号: | 93C46A-I/MS |

| 厂商: | Microchip Technology |

| 文件页数: | 7/36页 |

| 文件大小: | 0K |

| 描述: | IC EEPROM 1KBIT 2MHZ 8MSOP |

| 标准包装: | 100 |

| 格式 - 存储器: | EEPROMs - 串行 |

| 存储器类型: | EEPROM |

| 存储容量: | 1K (128 x 8) |

| 速度: | 2MHz |

| 接口: | Microwire 3 线串行 |

| 电源电压: | 4.5 V ~ 5.5 V |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 8-TSSOP,8-MSOP(0.118",3.00mm 宽) |

| 供应商设备封装: | 8-MSOP |

| 包装: | 管件 |

| 产品目录页面: | 1450 (CN2011-ZH PDF) |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

�� �

�

�

�93AA46A/B/C,� 93LC46A/B/C,� 93C46A/B/C�

�2.4� Erase�

�The� ERASE� instruction� forces� all� data� bits� of� the�

�specified� address� to� the� logical� ‘1’� state.� CS� is� brought�

�low� following� the� loading� of� the� last� address� bit.� This�

�falling� edge� of� the� CS� pin� initiates� the� self-timed�

�programming� cycle,� except� on� ‘93C’� devices� where� the�

�rising� edge� of� CLK� before� the� last� address� bit� initiates�

�the� write� cycle.�

�The� DO� pin� indicates� the� Ready/� Busy� status� of� the�

�device� if� CS� is� brought� high� after� a� minimum� of� 250� ns�

�low� (T� CSL� ).� DO� at� logical� ‘� 0� ’� indicates� that� programming�

�is� still� in� progress.� DO� at� logical� ‘� 1� ’� indicates� that� the�

�register� at� the� specified� address� has� been� erased� and�

�the� device� is� ready� for� another� instruction.�

�Note:� After� the� Erase� cycle� is� complete,� issuing�

�a� Start� bit� and� then� taking� CS� low� will� clear�

�the� Ready/� Busy� status� from� DO.�

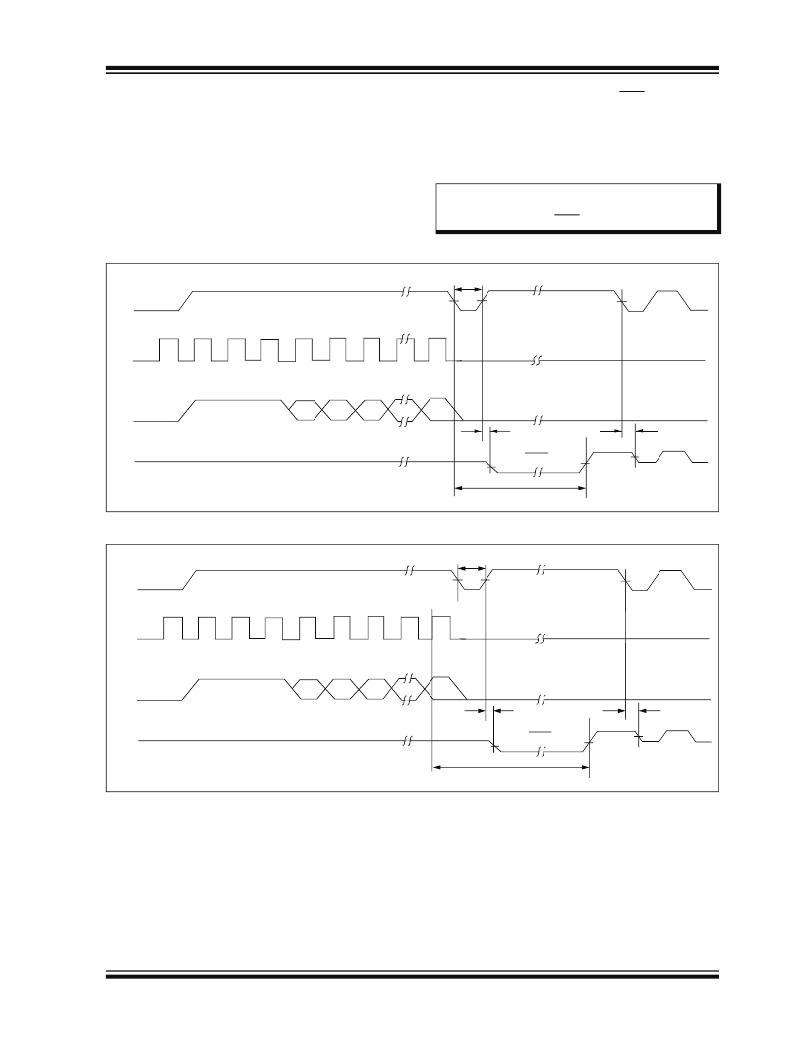

�FIGURE� 2-1:�

�CS�

�CLK�

�ERASE� TIMING� FOR� 93AA� AND� 93LC� DEVICES�

�T� CSL�

�Check� Status�

�DI�

�1�

�1�

�1�

�A� N�

�A� N� -1� A� N� -2�

�???�

�A0�

�T� SV�

�T� CZ�

�DO�

�High-Z�

�Busy�

�Ready�

�High-Z�

�T� WC�

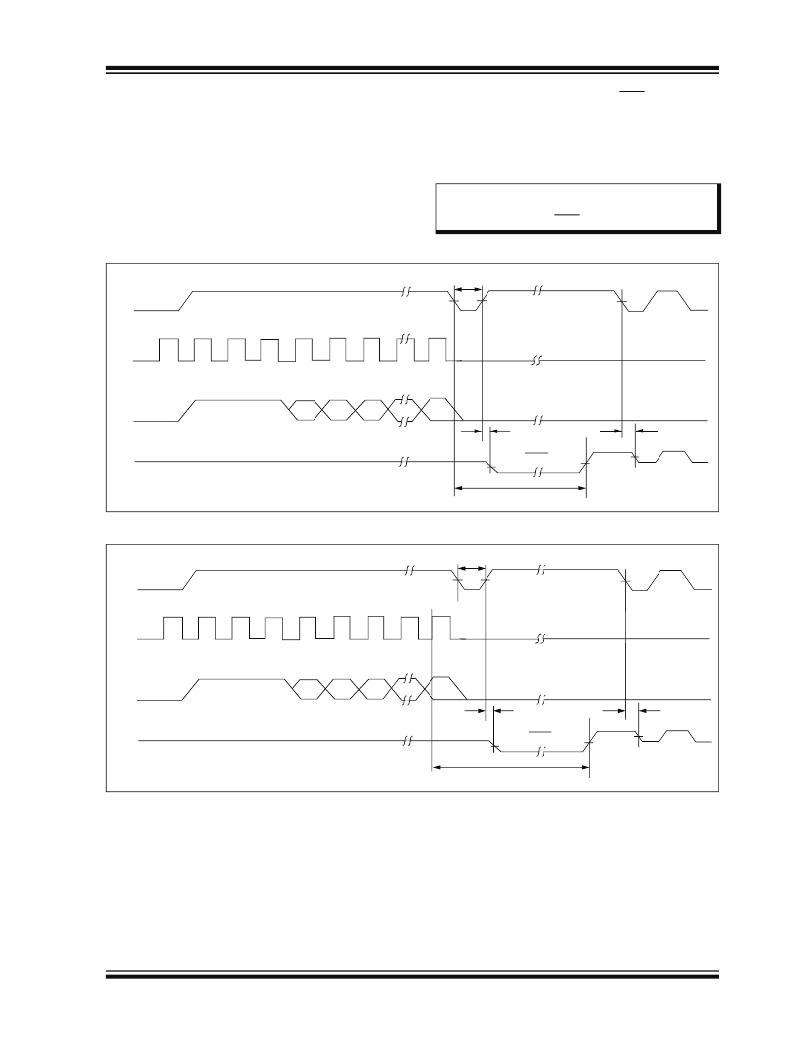

�FIGURE� 2-2:�

�ERASE� TIMING� FOR� 93C� DEVICES�

�T� CSL�

�CS�

�CLK�

�Check� Status�

�DI�

�1�

�1�

�1�

�A� N�

�A� N� -1� A� N� -2�

�???�

�A0�

�T� SV�

�T� CZ�

�DO�

�High-Z�

�Busy�

�Ready�

�High-Z�

�T� WC�

�?� 2002-2011� Microchip� Technology� Inc.�

�DS21749J-page� 7�

�相关PDF资料 |

PDF描述 |

|---|---|

| XC6SLX9-N3CSG324C | IC FPGA SPARTAN-6 324CSBGA |

| HMC50DRXS | CONN EDGECARD 100PS DIP .100 SLD |

| XC6SLX9-N3FTG256I | IC FPGA SPARTAN-6 256PBGA |

| XC6SLX9-N3CSG225I | IC FPGA SPARTAN-6 225CSBGA |

| RSA50DTMD-S664 | CONN EDGECARD 100PS R/A .125 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 93C46AK | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Microwire Serial EEPROM |

| 93C46AKI | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Microwire Serial EEPROM |

| 93C46AN | 制造商:Texas Instruments 功能描述: |

| 93C46AP | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Microwire Serial EEPROM |

| 93C46API | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Microwire Serial EEPROM |

发布紧急采购,3分钟左右您将得到回复。