- 您现在的位置:买卖IC网 > PDF目录42417 > 93C46B-I/SM 64 X 16 MICROWIRE BUS SERIAL EEPROM, PDSO8 PDF资料下载

参数资料

| 型号: | 93C46B-I/SM |

| 元件分类: | PROM |

| 英文描述: | 64 X 16 MICROWIRE BUS SERIAL EEPROM, PDSO8 |

| 封装: | 0.208 INCH, PLASTIC, SOIC-8 |

| 文件页数: | 6/12页 |

| 文件大小: | 211K |

| 代理商: | 93C46B-I/SM |

93C46B

2001 Microchip Technology Inc.

DS21172E-page 3

2.0

PIN DESCRIPTION

2.1

Chip Select (CS)

A high level selects the device; a low level deselects

the device and forces it into standby mode. However, a

programming cycle which is already in progress will be

completed, regardless of the Chip Select (CS) input

signal. If CS is brought low during a program cycle, the

device will go into standby mode as soon as the pro-

gramming cycle is completed.

CS must be low for 250 ns minimum (TCSL) between

consecutive instructions. If CS is low, the internal con-

trol logic is held in a RESET status.

2.2

Serial Clock (CLK)

The Serial Clock (CLK) is used to synchronize the com-

munication between a master device and the 93C46B.

Opcodes, addresses, and data bits are clocked in on

the positive edge of CLK. Data bits are also clocked out

on the positive edge of CLK.

CLK can be stopped anywhere in the transmission

sequence (at high or low level) and can be continued

anytime with respect to clock high time (TCKH) and

clock low time (TCKL). This gives the controlling master

freedom in preparing the opcode, address, and data.

CLK is a “Don't Care” if CS is low (device deselected).

If CS is high, but START condition has not been

detected, any number of clock cycles can be received

by the device, without changing its status (i.e., waiting

for a START condition).

CLK cycles are not required during the self-timed

WRITE (i.e., auto ERASE/WRITE) cycle.

After detecting a START condition, the specified num-

ber of clock cycles (respectively low to high transitions

of CLK) must be provided. These clock cycles are

required to clock in all required opcodes, addresses,

and data bits before an instruction is executed

(Table 2-1). CLK and DI then become don't care inputs

waiting for a new START condition to be detected.

2.3

Data In (DI)

Data In (DI) is used to clock in a START bit, opcode,

address, and data synchronously with the CLK input.

2.4

Data Out (DO)

Data Out (DO) is used in the READ mode to output

data synchronously with the CLK input (TPD after the

positive edge of CLK).

This pin also provides READY/BUSY status informa-

tion during ERASE and WRITE cycles. READY/BUSY

status information is available on the DO pin if CS is

brought high after being low for minimum chip select

low time (TCSL) and an ERASE or WRITE operation

has been initiated.

The status signal is not available on DO, if CS is held

low during the entire ERASE or WRITE cycle. In this

case, DO is in the HIGH-Z mode. If status is checked

after the ERASE/WRITE cycle, the data line will be high

to indicate the device is ready.

Note:

CS must go low between consecutive

instructions.

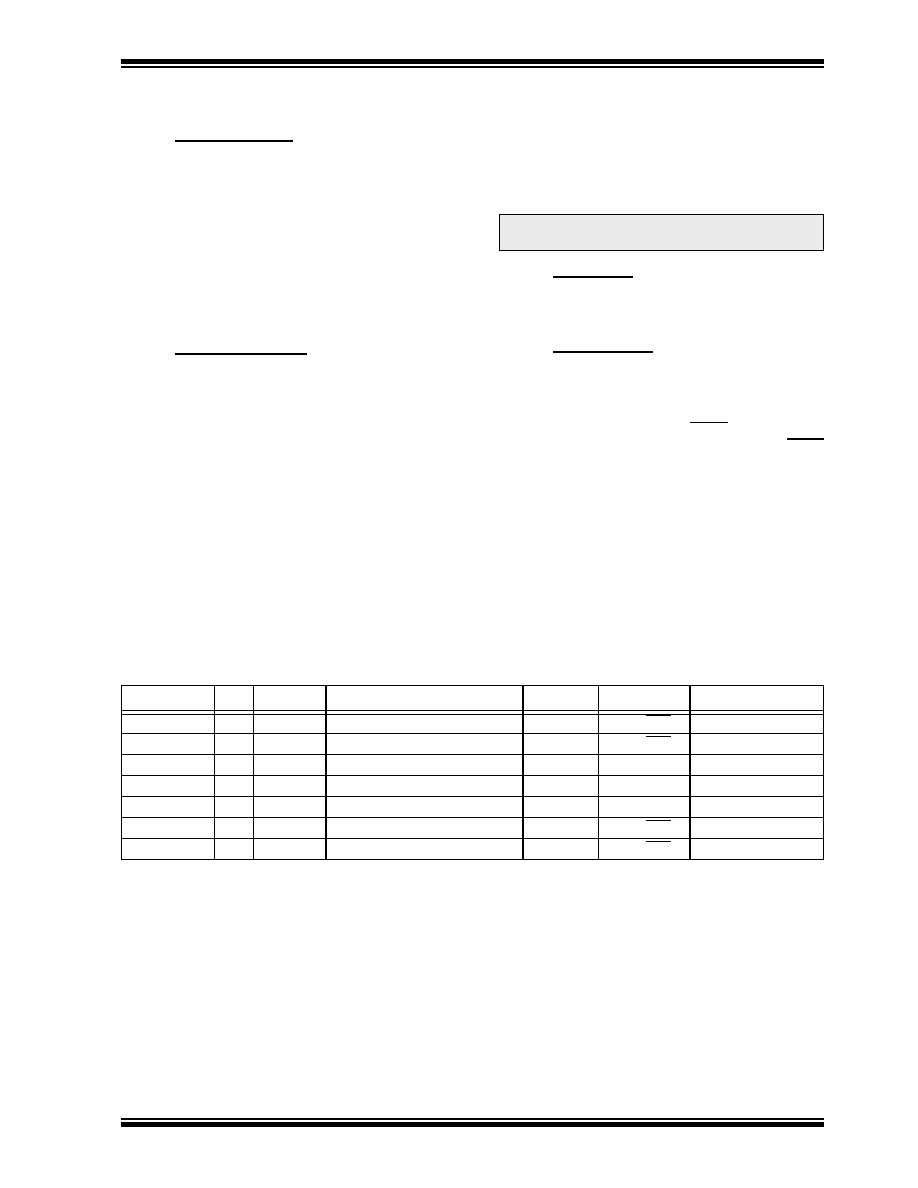

TABLE 2-1

INSTRUCTION SET FOR 93C46B

Instruction

SB

Opcode

Address

Data In

Data Out

Req. CLK Cycles

ERASE

1

11

A5

A4

A3

A2

A1

A0

—

(RDY/BSY)9

ERAL

1

00

1

0

XX

—

(RDY/BSY)9

EWDS

1

00

0

XX

—

HIGH-Z

9

EWEN

1

00

1

XX

—

HIGH-Z

9

READ

1

10

A5

A4

A3

A2

A1

A0

—

D15 - D0

25

WRITE

1

01

A5

A4

A3

A2

A1

A0

D15 - D0

(RDY/BSY)25

WRAL

1

00

0

1

X

D15 - D0

(RDY/BSY)25

相关PDF资料 |

PDF描述 |

|---|---|

| 93C46B/P | 64 X 16 MICROWIRE BUS SERIAL EEPROM, PDIP8 |

| 93C46BT-I/SM | 64 X 16 MICROWIRE BUS SERIAL EEPROM, PDSO8 |

| 93C46BT-E/SM | 64 X 16 MICROWIRE BUS SERIAL EEPROM, PDSO8 |

| 93C46B/PROC | 64 X 16 MICROWIRE BUS SERIAL EEPROM, PDIP8 |

| 93C46BI/SM | 64 X 16 MICROWIRE BUS SERIAL EEPROM, PDSO8 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 93C46B-ISN | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:1K 5.0V Microwire Serial EEPROM |

| 93C46B-IST | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:1K 5.0V Microwire Serial EEPROM |

| 93C46BP | 制造商:Microchip Technology Inc 功能描述: |

| 93C46B-P | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:1K 5.0V Microwire Serial EEPROM |

| 93C46B-SM | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:1K 5.0V Microwire Serial EEPROM |

发布紧急采购,3分钟左右您将得到回复。